湖南大学_数电实验_模型机设计_CPU设计_verilog_课程实验报告

本学期的数电课程实验就是使用verilog进行模型机设计,由四次小实验构成,最后一次实验验收要求使用quartus做出一个模型机。其主要核心就是理解和设计CPU。

本学期的数电课程实验就是模型机设计,由四次小实验构成,最后一次实验验收要求使用quartus做出一个模型机。

该实验的重要性:该实验的核心在于基于实验指导书设计CPU,从而帮我们理解CPU的工作原理。而CPU作为计算机的核心部件,可以帮助我们引入一个全新的视角来理解操作系统和计算机系统(为之后的课程打基础)。所以建议大家在做这个实验之前,先花时间弄清楚,CPU究竟是怎么工作的。

以下为实验报告,内容较为详细,仅供参考,如有错误敬请斧正!

目录

5.1 从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

一、设计目的

本课程力图以“培养学生现代数字系统设计能力”为目标,贯彻以 CPU 设计为核心,以层次化、模块化设计方法为抓手的组织思路,培养学生设计与实现数字系统的能力。 本设计要求在进行了多个单元实验后,综合利用所学的理论知识, 结合在单元实验中所积累的成果(包括已经设计好的功能部件和调试方法),设计出一个简易计算机系统。

二、设计内容

⚫ 按给定的数据格式和指令系统,使用 EDA 工具设计一台用硬连线逻辑控制的简易计算机系统;

⚫ 要求灵活运用各方面知识,使得所设计的计算机系统具有较佳的性能;

⚫ 对所做设计的性能指标进行分析,整理出设计报告。

三、 详细设计

3.1 设计的整体架构

①模型机工作的基本形式

同步电路,采用串行工作方式,即“读取—执行—再读取—再执行……”。

②模型机的数据格式

数据字采用 8 位二进制定点补码表示,其中最高位(第 7 位)为符号位,小数点可视为最左或最右,其数值表示范围分别为:-1≤X<+1 或-128≤X<+127。

③模型机的指令系统(基于数据格式)

注:我们老师更改过跳转指令的操作码,如下图红色标注)

④模型机的寻址方式

指令的高 4 位为操作码,低 4 位分别用 2 位表示目的寄存器和源寄存器的编号, 或表 示寻址方式。共有 2 种寻址方式。

(1)寄存器直接寻址

![]() 当 R1 和 R2 均不是“11”时,R1 和 R2 分别表示两个操作数所在寄存器的地址(寄存器 编号),其中 R1 为目标寄存器地址,R2 为源寄存器地址。

当 R1 和 R2 均不是“11”时,R1 和 R2 分别表示两个操作数所在寄存器的地址(寄存器 编号),其中 R1 为目标寄存器地址,R2 为源寄存器地址。

(2)寄存器间接寻址

![]() 当 R1 或 R2 中有一个为“11”时,表示相应操作数的地址在 C 寄存器中。

当 R1 或 R2 中有一个为“11”时,表示相应操作数的地址在 C 寄存器中。

⑤模型机的数据通路及说明

计算机的工作过程可以看作是受控下的数据流动,数据流所经过的路径称作机器的数据通路。数据通路不同,指令执行所经过的操作过程就不同,机器的结构也就不一样。

1. 取指令的过程

指令计数器中的内容(即下一条要执行的指令的地址),经选择器送至 RAM 的 地址输入端(开始执行,先把要执行的指令地址传过去);在 DL 和地址输入的共同作 用下,指令在时钟的上升沿从 RAM 中被读出送至总线 BUS 上,在 LD IR 信号的控 制下,BUS 上的指令在时钟的下降沿载入到指令寄存器 IR 中;然后指令计数器加 1 (这一条执行完,计数器加 1,为下一次可以直接用做准备)。

2. 执行指令--传送类指令

(a)寄存器之间的传送 MOVA R1,R2

要求完成的操作为(R2)→R1,执行过程为: 由 R2 的编码通过 RAA1、RAA0 从通用寄存器组 A 口读出 R2 的内容,在 S3~S0 和 M 的控制下,经 ALU 送入总线 BUS;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。

(b)寄存器到内存的传送 MOVB M,R2

要求完成的操作为(R2)→(C),执行过程为: 由 M 的编码 11 通过 RWBA1、RWBA0 从通用寄存器 B 口读出 C 寄存器中的地址,在 MADD=2 的控制下,地址通过选择器到达存储器 RAM 的地址输入端;由 R2 的编码通过 RAA1、RAA0 从通用寄存器组 A 口读出 R2 的内容,在 S3~S0 和 M 的控制下,经 ALU 送 入总线 BUS,并在/CS 和 XL 控制下将 BUS 上的数据写入存储器 RAM。

(c)内存到寄存器的传送 MOVC R1,M

要求完成的操作为((C))→R1,执行过程为: 由 M 的编码 11 通过 RAA1、RAA0 从通用寄存器 A 口读出 C 寄存器中的地址,在 MADD=1 的控制下,地址通过选择器到达存储器 RAM 的地址输入端,/CS 和 DL 使数据出 现在 BUS 上;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。

3. 执行指令--算术逻辑运算指令

将编码01(由RAA1、RAA0提供)对应的寄存器B中的数据并从通用寄存器组S口读出;

同时将编码00(由RWBA1、RWBA0提供)对应的寄存器A中的数据并从通用寄存器组D口读出;

在S3-S0和M的控制下,2个操作数在ALU中运算后经移位逻辑送入总线BUS;

由/WE(0)控制将BUS上的数据在时钟下降沿写入编码00(由RWBA1、RWBA0提供)对应的寄存器A中。

ADD、SUB指令影响状态位Cf和Zf。

4. 执行指令—转移类指令

(a)JMP,取好指令后,开始一个新的时钟周期,假设上一个取址位置为RAM中的00000000,在取好指令的同时,在pc_inc为1和时钟下降沿的共同作用下,PC现在存放的地址为00000001。执行指令期间,madd[1..0]保持不变,还是00,于是这个00000001通过选择器到达RAM的地址输入端,然后DL为1,在时钟上升沿到来的时候将该地址对应的内容传送到总线上,然后此时pc_ld为1, 在时钟下降沿到来瞬间,将总线上的数据写入到PC中。

(b)JC,取好指令后,开始一个新的时钟周期,假设上一个取址位置为RAM中的00000000,在取好指令的同时,在pc_inc和时钟下降沿的共同作用下,现在存放的地址为00000001。和JMP比起来,多了一个C为1的条件。若C=0,pc_inc为1,在时钟下降沿PC存储的地址变为00000010。也就是说跳过了00000001地址所存储的指令。

(c)JZ,与JC的区别就在于,判断条件为Z是否为1.

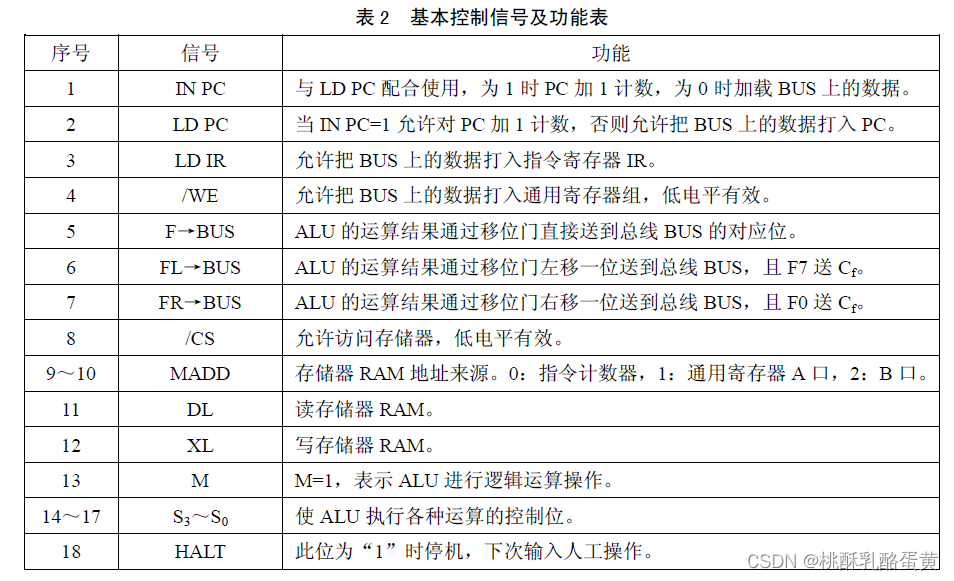

⑥控制信号

⑦顶层电路图

3.2各模块的具体实现

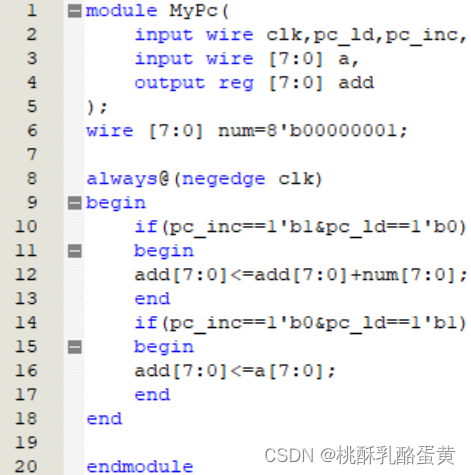

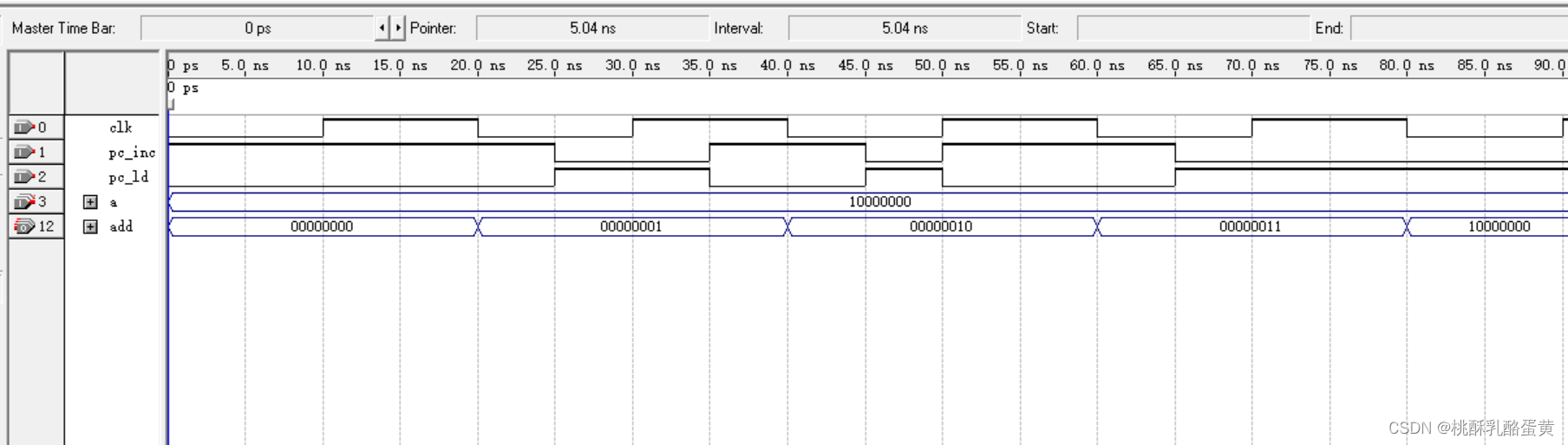

模块1:指令计数器PC

【模块的封装】

【功能实现及接口设计】

功能描述:

指令计数器PC存储当前指令在RAM中存放的地址。 CPU执行一条指令,根据PC中存放的指令地址,将指令从RAM读出写入指令寄 存器IR中,此过程称为“取指令”。在每条指令读取后,指令计数器PC中的地址 自动加1,指向下一条指令在RAM中的存放地址。跳转指令如JMP、JZ、JC让程序 跳转至指定地址去执行,这时PC需要装载跳转地址。模型机的的指令计数器PC是一个8位计数器,其的功能如下:

使用Verilog进行实现:

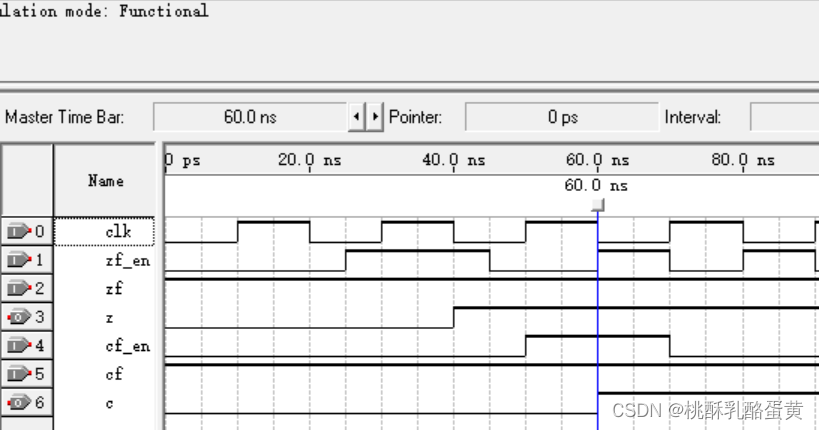

【功能的仿真验证】

模块2:多路复用器MUX

【模块的封装】

【功能实现及接口设计】

功能描述:

多路复用器是一个组合电路,它可以从多个输入中选择一个输入,并将信息 直接传输到输出。选择哪一条输入线由一组输入变量控制,它们被称为选择输入。 S D S D 通常, 2 n 条输入线要 n 个选择输入,选择输入的位组合决定选择哪个输入线。 8 重 3-1 多路复用器有 3 个输入 1 个输出,每个输入和输出都是 8 位,所以 称之为 8 重,MADD 选择将哪个输入传至输出。其的功能及封装如下:

使用Verilog进行实现:

【功能的仿真验证】

模块3:随机存储器RAM

【模块的封装】

【功能实现及接口设计】

功能描述:

随机存储器RAM是与CPU直接交换数据的内部存储器,也叫主存(内存)。它 可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临 时数据存储媒介。 存储元是构成存储器的存储介质,它可存储一个二进制位。由若干个存储元 组成一个存储单元,然后再由许多存储单元组成一个存储器。一个存储器包含许 多存储单元,每个存储单元可存放一个字节。每个存储单元的位置都有一个编号, 即地址,一般用十六进制表示。一个存储器中所有存储单元可存放数据的总和称 为它的存储容量。比如,一个存储器的地址码由8位二进制数(即2位十六进制数) 4 组成,则可表示2的8次方,即256个存储单元地址,每个存储单元存放一个字节, 则该存储器的存储位数为256×8,即2Kbit。

其封装及功能如下图

实现方式:

本实验可采用Quartus中已有的参数化模块来定制RAM功能,在【Symbol】元 件库的【megafunctions】|【storage】中选择LPM_RAM_IO,创建RAM时加载初始 化数据文件,初始化文件的创建过程是:【File】|【New】|【Memory Initialization File】。

【功能的仿真验证】

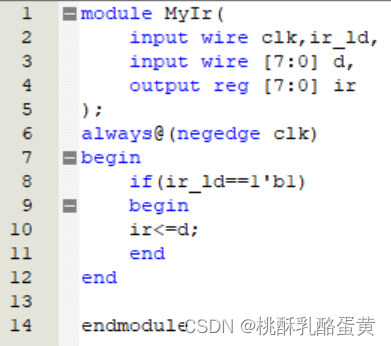

模块4:指令寄存器IR

【模块的封装】

【功能实现及接口设计】

功能描述:

指令寄存器(IR,Instruction Register)用于暂存当前正在执行的指令。 指令寄存器将总线送来的指令存入8位寄存器中,但并不是每次总线上的数据都 需要寄存,因为数据总线上有时传输指令,有时传输数据。当控制信号IR_LD为1 时,指令寄存器在时钟信号CLK的下降沿将总线传输的指令写入寄存器。 指令寄存器IR是一个8位寄存器。

其功能及封装如下:

使用Verilog进行实现:

【功能的仿真验证】

模块5:SM

【模块的封装】

【功能实现及接口设计】

功能描述:

模型机中所有指令都要求两个周期完成,其中一个周期取指令,一个周期执 行指令。如何区分当前周期是取指令还是执行指令呢?这就需要SM配合。SM为0 是取指令周期;SM为1是执行指令周期。

SM的功能如下:

使用Verilog进行实现:

【功能的仿真验证】

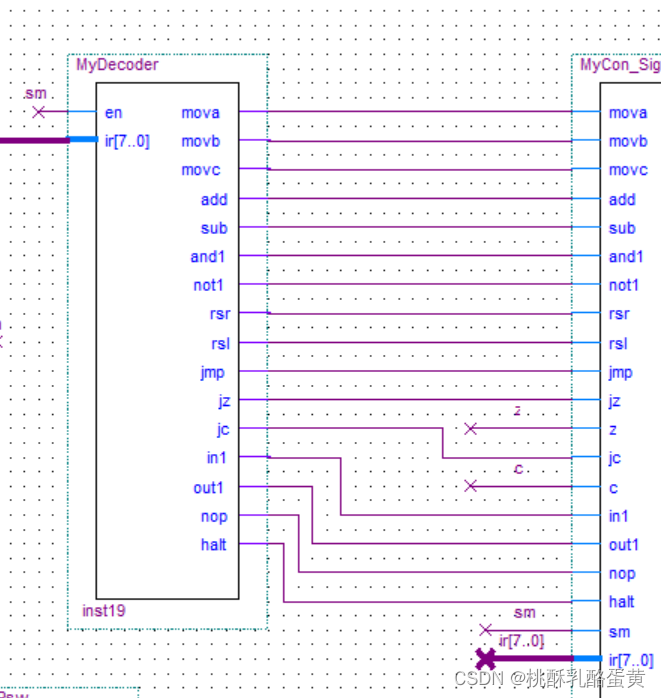

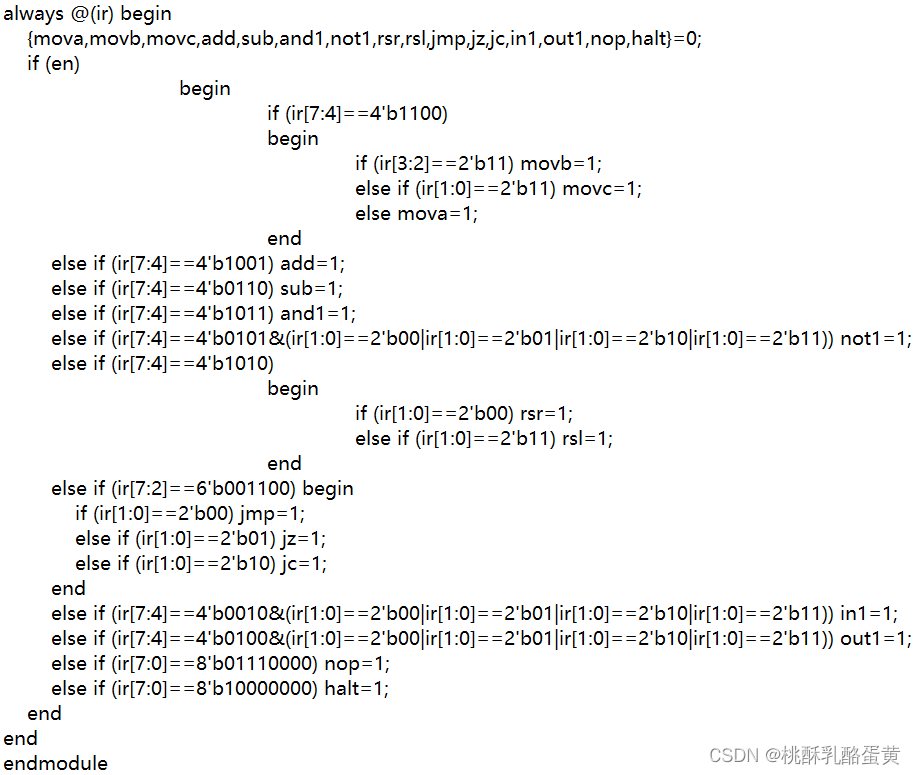

模块6:指令译码器Decoder

【模块的封装】

【功能实现及接口设计】

功能描述:

指令译码器是根据指令系统表中的指令编码,对输入的 8 位指令进行解析, 判定是哪条指令,则对应指令的输出为 1,否则输出为 0。

en 为使能信号,ir[7..0]是 8 位指令 编码,输出是对应的 16 条指令。引脚之间的相互关系如下表所示:

使用Verilog进行实现:

感谢kilansa朋友的提示!在此进行一个二次修改。

【功能的仿真验证】

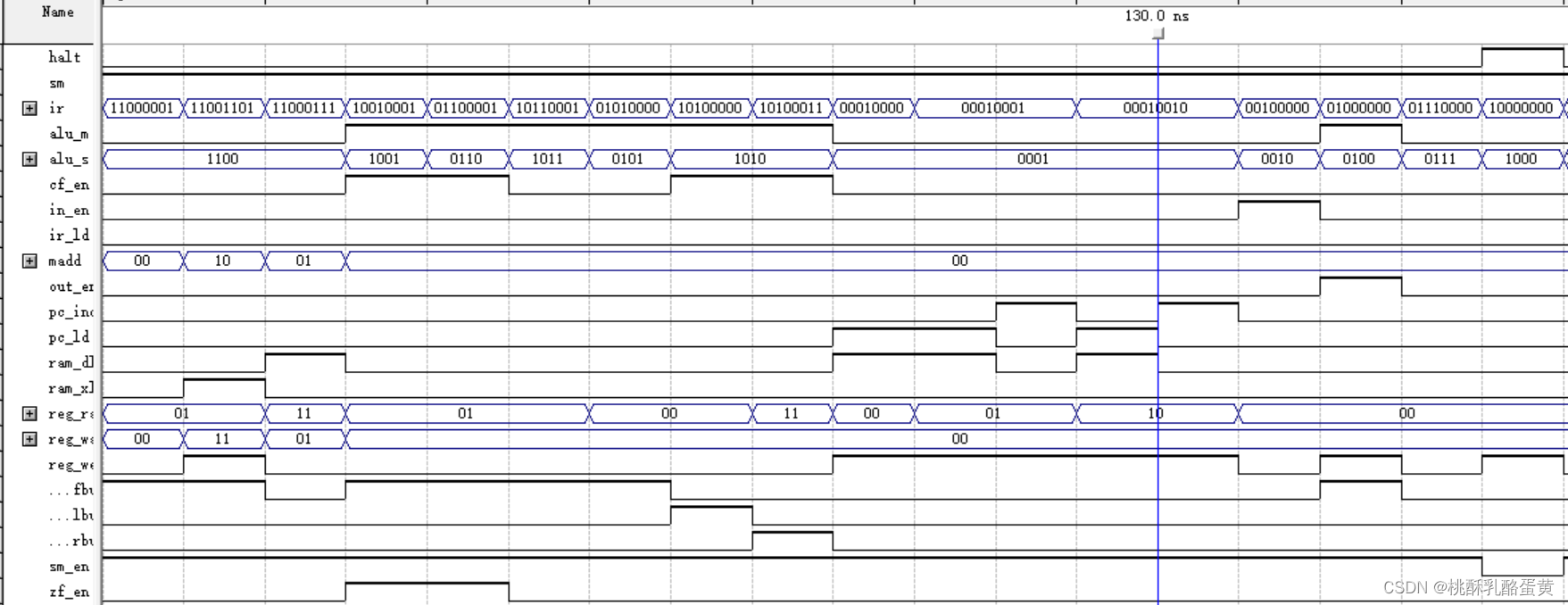

模块7:控制信号产生逻辑Con_Signal

【模块的封装】

【功能实现及接口设计】

功能描述:

控制信号产生逻辑接收指令译码器的输出,在 SM、IR[7..0]以及状态位 Cf 和 Zf 的配合下产生每个模块所需要的控制信号。

使用Verilog进行实现:

【功能的仿真验证】

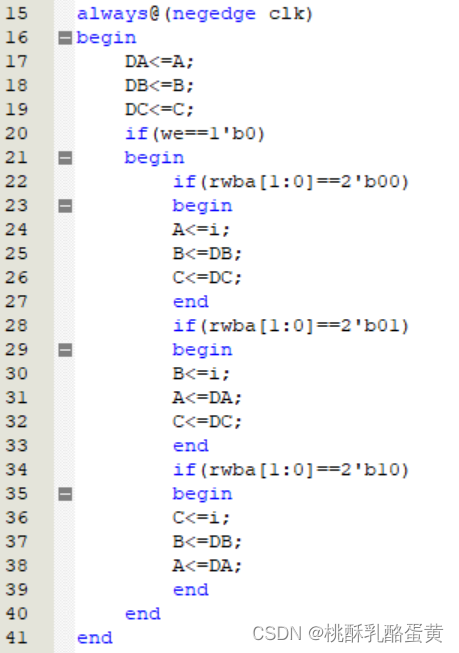

模块8:通用寄存器组Reg

【模块的封装】

【功能实现及接口设计】

功能描述:

寄存器主要用来保存操作数和运算结果等信息,从而节省从RAM中读取操作 数所需占用总线和访问存储器的时间。 模型机的通用寄存器组包含3个8位寄存器A、B、C,可对这3个寄存器进行读 写操作。

其功能如下:

使用Verilog进行实现:

【功能的仿真验证】

模块9:ALU

【模块的封装】

【功能实现及接口设计】

功能描述:

算术逻辑运算类指令:

ADD R1, R2

SUB R1, R2

AND R1, R2

NOT R1

这类指令的执行过程为:

由 R2 的编码通过 RAA1、RAA0 从通用寄存器组 S 口读出 R2 的内容,由 R1 的编码通过 RWBA1、RWBA0 从通用寄存器组 D 口读出 R1 的内容,在 S3~S0 和 M 的控制下,实现运算,经移位逻辑送入总线 BUS;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。其中 ADD 和 SUB 指令影响状态位 Cf 和 Zf。

ALU 除了要完成 ADD、SUB、AND、NOT 运算外,还需在 MOVA、MOVB、 RSR、RSL 和 OUT 五条指令执行时,提供将数据传送至总线的数据通路。

其功能实现如下图所示:

使用Verilog进行实现:

【功能的仿真验证】

模块10:移位逻辑Shift

【模块的封装】

【功能实现及接口设计】

功能描述:

移位指令: RSR R1(右移) RSL R1(左移)

这类指令的执行过程为: 由R1的编码通过RWBA1、RWBA0从通用寄存器组D口读出R1的内容,在 S3~S0和M的控制下通过ALU,经移位逻辑循环右移或循环左移后送入总线BUS; 再由/WE控制和R1的编码选择RWBA1、RWBA0,将BUS上的数据写入通用寄存器R1。 移位逻辑需要实现RSR、RSL操作,还在MOVA、MOVB、ADD、SUB、AND、 NOT、OUT指令执行时,将数据传输至BUS总线。

RSR循环移位操作如下:

引脚之间的相互关系如下:

使用Verilog进行实现:

【功能的仿真验证】

模块11:状态寄存器PSW

【模块的封装】

【功能实现及接口设计】

功能描述:

状态寄存器PSW是计算机系统的核心部件——运算器的扩展部分。本模型机 PSW用来存放ADD、SUB、RSR、RSL指令执行结果的状态标志,如有无借位进位(C)、 结果是否为零(Z)。有些机器也将PSW称为标志寄存器FR(Flag Register)。 本模型机PSW是一个2位寄存器。

其功能如下:

使用Verilog进行实现:

【功能的仿真验证】

模块12:输入IN

【模块的封装】

【功能实现】

功能描述:在使能信号有效的情况下,将输入通过总线传输到寄存器。

实现:基于元件库里的三态门“TRI”进行实现。

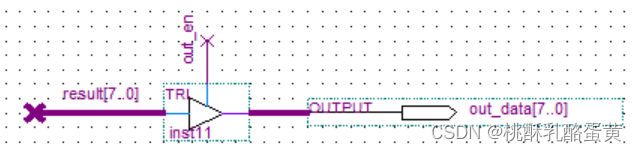

模块13:输出OUT

【模块的封装】

【功能实现】

功能描述:在使能信号有效的情况下,将总线上的数据(数据来自于寄存器)输出。

实现:基于元件库里的三态门“TRI”进行实现。当使能信号为0时,输出均为高阻态。

注:使用三态门可以有效地避免总线冲突。

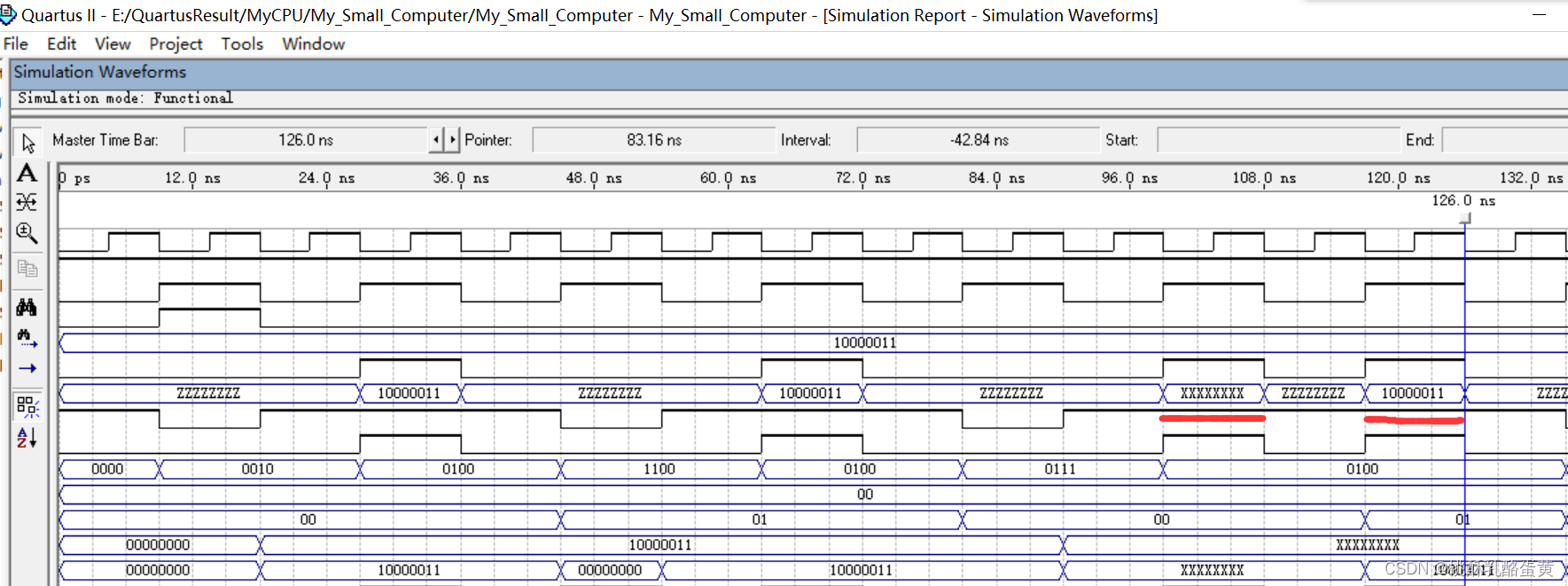

四、系统测试

详见文章(含测试所用指令集合):https://mp.csdn.net/mp_blog/creation/editor/125415692

五、实验总结、必要体会及建议

5.1 从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

【需要掌握的理论】

Verilog的基本语法、组合电路和时序电路的编写、模型机的工作过程、下板子的操作

【遇到的困难及解决的方法】

困难1:通用寄存器组由于编写代码时不当,导致前前后后修改了七八次。

解决方法:每一次更改后让模型机执行不同的与寄存器有关的指令,看是哪一个模块出现了问 题,然后回去看实验指导书,然后再看代码实现是否正确。

印象深刻的修改之一------挥之不去的reg中的锁存器

(这样子会有锁存器)

(这样子会有锁存器)

(需要更改为此)

(需要更改为此)

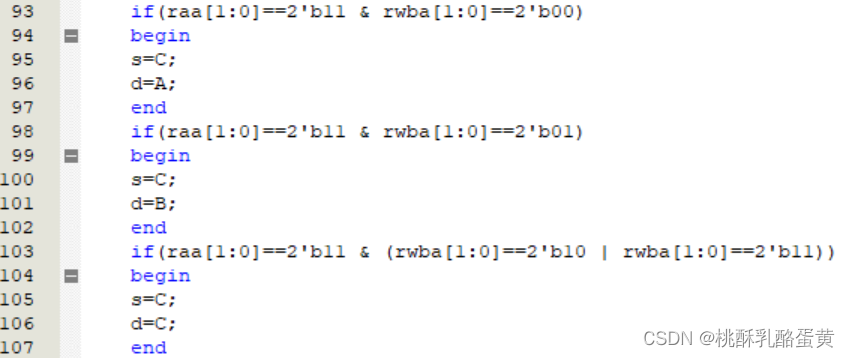

印象深刻的修改之一------“11”认知不足,10的确是C寄存器,但是不代表只有“10”才能够使用C寄存器,“11”也可以。

困难2:数组下标和向量下标定义搞混

解决方法:百度查找

困难3:对于“&&”和“||”和“&”和“|”的使用时机不清楚

解决方法:询问老师。

最后结果,全部都用按位与或者按位或。

困难4:拐角的线无法命名。

7:26 PM

7:26 PM

解决方法:改成两个端口使用命名法连接。

困难5: “Error:Can’t stimulate mismatched node types ”无法进行仿真验证

解决方法:先百度,百度无果,将该语句放到百度翻译进行翻译。询问同学和老师原因。

最后的解决方案:给输出引脚换一个名字。输出引脚命名最好不要与文件中的命名重复,确保每一个命名都独一无二。

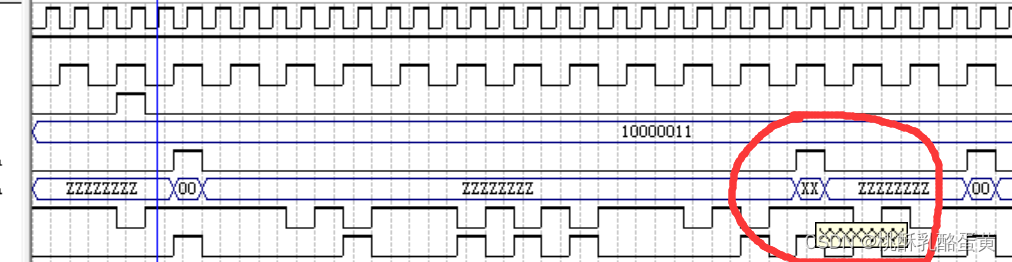

困难6:nop指令执行完之后,寄存器内的值会变为未知,如下

解决方法:新建一个mif文件,对其功能进行逐一排查。

发现A变成了未知量,但是B还在,为什么呢?回想刚刚,也是A变成了未知。

发现问题好像出现在we控制信号,于是回到代码代码检查,发现自己忘记we是低电平有效了,所以在写代码的时候没有把we考虑进去,在这个错误代码的运行下,we为0是有效的,且rwba[1..0]为00,所以会把总线上的数据写入,但是总线上现在没有数据,所以就变成了未知量。修改代码如下。

【经验教训】

{一些小错误}

连线之前要先对引脚进行命名,否则会出现这样子的结果。

仿真验证只认同名波形

{如何下板子}

感谢万能的群友,感谢每一位愿意分享的朋友。

{做的过程大总结}

首先,做这个实验之前应该要先搞清楚模型机的工作原理,了解实现模型机要用到的工具(Verilog基本语法、quartus的基本使用),然后对其进行学习,在学习之前可以先百度一下一些学者对这些学习内容的建议。

其次,在实现过程一定要认真的阅读实验指导书,不然会因为细节而犯下很多错误。譬如说,因为没有好好阅读导致只记得rwba或者raa在接收01信号时会用到C寄存器,而忘记在接收11信号时也会用到C寄存器,导致后面的波形仿真一直无法出现正确结果。

最后,在连线之前,要先对各个部件的功能进行检查,看其与指导书是否一致。在连线时不要一下子连很多个模块,而是先将几个模块进行连接,对其进行功能仿真观看波形输出是否正确。每检查一条数据通路就在图上进行标注

,这样可以大大提高工作效率。当发现有错误的时候,从错误出发,先去检查代码是否有问题,然后再检查连线。总之,把细节做到位,是防止最后出错的最好方法。我觉得我很幸运,虽然我在纠正细节上花了很多的时间,但是最后我连出来的模型机是对的。没有bug狂出真的太幸运了,我要一直努力。

,这样可以大大提高工作效率。当发现有错误的时候,从错误出发,先去检查代码是否有问题,然后再检查连线。总之,把细节做到位,是防止最后出错的最好方法。我觉得我很幸运,虽然我在纠正细节上花了很多的时间,但是最后我连出来的模型机是对的。没有bug狂出真的太幸运了,我要一直努力。

{验证过程中很重要的一步}

设计mif文件时,可以使用EXCEL表格进行罗列指令和分析结果,这样做起来思路会很清晰。

恭喜你读到文末,这一篇文章凝聚了一学期的努力,一开始真的无从下手,第一次也是请教同学的,后面自己尝试做了之后发现还是比较简单的,所以希望屏幕面前的你也能收获超幸福的满足感!如果有帮到你的话,可以点赞收藏一下噢!后续会出“从CPU的角度来看操作系统”的相关系列文章,大家感兴趣的可以关注一下我哦~

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)