数字电子技术 实验一

实验一一、实验目的学习multisim仿真软件的基本操作和分析方法使用multisim对数字电路进行功能验证二、实验内容利用基本逻辑门对半加器进行电路设计和仿真验证译码器74LS138N的逻辑功能三、实验步骤1. 半加器电路仿真(1)半加器 两个1位二进制数相加,没有考虑低位的进位,只考虑自身,称为半加,实现半加运算的逻辑电路称为半加器。 半加器的逻辑表达式:...

实验一

一、实验目的

- 学习multisim仿真软件的基本操作和分析方法

- 使用multisim对数字电路进行功能验证

二、实验内容

- 利用基本逻辑门对半加器进行电路设计和仿真

- 验证译码器74LS138N的逻辑功能

三、实验步骤

1. 半加器电路仿真

(1)半加器

两个1位二进制数相加,没有考虑低位的进位,只考虑自身,称为半加,实现半加运算的逻辑电路称为半加器。

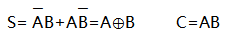

半加器的逻辑表达式:

其中输入为A和B,输出S代表和,输出C表示进位

| 输 | 入 | 和 | 进位 |

|---|---|---|---|

| A | B | S | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

半加器的逻辑图如下所示:

实验过程中,我们选取异或门74LS86D和与门74LS08D实现半加器的逻辑功能。

(2)器件选取

电源和地:点击绘制的元器件,选择Sources组下的POWER_SOURCES,选取元器件列表下的VCC电源和DGND地。

逻辑开关:在Basic->SWITCH->SPDT,放置两个单刀双掷开关控制A、B的高低电平。

异或门的选取:TTL->74LS->74LS86D。

与门的选取:TTL->74LS->74LS08D。

逻辑探头:在Indicators->PROBE下选择两个来作为输出的指示灯。

虚拟仪器表选择字信号发生器XWG1和逻辑分析仪XLA1。

(3)仿真分析

放置元器件并进行连接,构成半加器的仿真测试电路,点击仿真开始,开关A、B表示不同的输入数值,接高电平VCC表示输入为1,接低电平低表示输入为0,输出结果指示灯亮为1,按照表1所示真值表进行仿真测试,观察输出结果,填写表1的输出结果。

利用字信号发生器和逻辑分析仪搭建输入/输出信号仿真电路,点击仿真开始,激活电路,观察电路输入输出波形与半加器真值表是否一致。

2. 译码器74LS138N的功能验证仿真

(1)3位二进制译码器

74LS138N是一个集成的3线-8线译码器,它的输入是3位二进制代码A、B、C,而3位二进制代码可表示8种不同的状态,所以输出的必须是8个译码信号,译码器还设置了三个使能输入端G1、G2A和G2B 。

图2所示是译码器74LS138N的逻辑符号,它的功能表如表2所示。

| 使 | 能 | 端 | 输 | 入 | 端 | 输 | 出 | 端 | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| G1 | G2A | G2B | C | B | A | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| 0 | x | x | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| x | 1 | x | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| x | x | 1 | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

由图2可知,此译码器有3个输入端,可以输出8种状态,由二进制代码表示,二进制代码从高到低为C、B、A,输入三位代码可译出对应的8个输出Y0~Y7,输出信号是低电平有效。(例如输入代码000,输出端Y0被选中,输出信号低电平0,其余输出信号为高电平1)。译码器设置了三个使能端,即G1、G2A和G2B,当G1=1,且G2A=G2B=0时,译码器工作。当使能信号 G1G2AG2B≠100时,禁止译码,输出全为高电平。

(2)元器件选择

电源和地:点击绘制的元器件,选择Sources组下的POWER_SOURCES,选取元器件列表下的VCC电源和DGND地。

逻辑开关:在Basic->SWITCH->SPDT,放置三个单刀双掷开关控制使能端的状态。

译码器:TTL->74LS,选取74LS138N。

逻辑探头:Indicators->PROBE,选取8个指示灯。

虚拟仪器表选取选择字信号发生器XWG1和逻辑分析仪XLA1。

(3)仿真分析

连接器件,将三个使能端连接单刀双掷开关,字信号发生器连接输入端产生输入信号,输出端连接指示灯,构建译码器的功能仿真电路,点击仿真开始,按照功能表进行仿真,观察指示灯结果,并填写完整功能表。

将输入输出端接入逻辑分析仪,点击仿真开始,观察分析仪显示的输入/输出波形。

四、实验报告

1. 半加器电路仿真

1.1 半加器的仿真电路图和波形图

仿真电路图:

波形图:

1.2 实验原理

半加器的原理为输入同时为1时,和为0,进位为1;输入同时为0时,和、进位都为0;输入为1,0时,和为1,进位为0。对于和应当采用异或门,进位则采用与门。

1.3 实验设计思路

① 先实现自主控制的电路图,确定电路实现所需元件,将所有元件添加到设计中,此实验需要高电压、低电压各一个、开关两个、异或门一个、与门一个指示灯两个;

② 对于各个元件进行重命名、快捷键操作等设计;

③ 根据实验原理进行电路连接,先连接电源与开关,再连接开关与异或门、与门,最后连接异或门、与门和指示灯;

④ 连接完成后进行运行测试,控制开关的开合状态,记录指示灯的开闭状态;

⑤ 进一步实现仿真设计,选择字分析仪、逻辑分析仪以及相关组合电路原理,根据之前的电路图原理进行连接;

⑥ 对于字分析仪进行设置,显示—二进制、控件—设置—预设模式—上数序计时器、缓冲器—(n为输入源的数量),频率及其他设置一般不改动;

⑦ 设置确定后点击运行,双击逻辑分析仪即可进行结果的波形图查看;

⑧ 自主电路图、波形图验证设计思路的元件部署进行优化美观处理。

1.4 运行效果及分析

自主电路设计运行正常无误,对比逻辑分析仪的波形图结果一致,电路图及波形图见上。

运行时根据二进制的升序进行控制,比如000、001、010、011……此题中,半加器中开关的开表示1、闭合表示0。具体控制顺序与实际显示情况如下:

| 开关A | 开关B | 指示灯S | 指示灯C |

|---|---|---|---|

| 低电压 | 低电压 | 不亮 | 不亮 |

| 低电压 | 高电压 | 亮 | 不亮 |

| 高电压 | 低电压 | 亮 | 不亮 |

| 高电压 | 高电压 | 不亮 | 亮 |

1.5 总结

自主电路设计时,对于开关与电源的连接一开始不太理解,后来发现远来是控制组合电路输入的不同状态,其他连接基本没有问题。

在字分析仪与逻辑分析仪设计进行波形图设计时,波形图开始一直为高电压状态,与实际情况不符。后来发现是字分析仪未设置好缓冲区大小,

半加器的电路设计本质并不复杂,但是由于这是第一次使用Multisim进行电路实现设计所以花费了很多时间。实现电路设计一定要先想好思路,不能走一步看一步,这样会浪费很多莫名的时间。而且容易走很多不必要的错路。

可以先画一个简易的流程图与电路原理图,之后根据这些图表再进行设计可以事半功倍,而且感觉思路特别清晰。

2. 译码器74LS138N的功能验证仿真

2.1 译码器74LS138N的仿真电路图和波形图

仿真电路图:

波形图:

2.2 实验原理

当两个选通输入G2A和G2B 为低时, 它可将3个二进制编码的输入译成8 个互相独立的输出之一。实现解调功能的办法是:用3个输入线写出输出线的地址,使得在一个选通输入为低时数据通过另一个选通输入。当任何一个选通输入是高时,所有输出都为高。

2.3 实验设计思路

① 先实现自主控制的电路图,确定电路实现所需元件,将所有元件添加到设计中,此电路需要低电压、高电压各一个,开关六个、组合逻辑电路一个、指示灯六个;

② 对于各个元件进行重命名、快捷键操作等设计;

③ 根据实验原理进行电路连接,先连接电源与开关,再连接开关与逻辑电路,最后连接组合电路元件与指示灯;

④ 连接完成后进行运行测试,控制开关的开合状态,记录指示灯的开闭状态;

⑤ 进一步实现仿真设计,选择字分析仪、逻辑分析仪以及相关组合电路原理,根据之前的电路图原理进行连接;

⑥ 对于字分析仪进行设置,显示—二进制、控件—设置—预设模式—上数序计时器、缓冲器—(n为输入源的数量),此实验为0064,频率及其他设置一般不改动;

⑦ 设置确定后点击运行,双击逻辑分析仪即可进行结果的波形图查看;

⑧ 对波形图设计电路优化处理,输入源设置为随机信号,三个使能端可以默认设置为100,这样可以更方便查看指定灯的变化情况,不过实际情况却并不完全,所以仅为辅助验证电路。

⑨ 自主电路图、波形图验证设计思路的元件部署进行优化美观处理。

2.4 运行结果与分析

当使能端G2A为1或者使能端G2B为1或者使能端G1为0时,不管三个信号源输入是什么,所有指示灯都是亮的。只有当使能端G1为1,G2A为0,G2B为0时,改变三个输入源的信号,每次会有一个指示灯熄灭。

辅助的波形图设计电路如下,此图更方便与自主控制电路图进行效果验证,但由于输入不完全,只能作为辅助使用。

2.5 总结

译码器74LS138N的功能验证主要在于理解使能端对整个电路的输出控制。此电路的设计因为有了第一个半加器实验设计的经验所以思路清晰了很多,也少走了很多弯路。

需要注意的就是字分析仪中的缓冲区大小设计以及整个思路的流畅性,最好先考虑清楚所有情况否则很容易有遗漏之处。

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)