Verilog学习之数据常量表达与位宽

Verilog学习之数据常量表达与位宽Verilog的表示形式Verilog中整数,整型常量即整常数有以下4种进制表示形式:1)二进制(b或B);2)十进制(d或D);3)十六进制(h或H);4)八进制(o或O)。数字表达式分为三种:1)<位宽><进制><数字>,这是最完整的形式。2)<进制><数字>,数字的位宽采用默认...

本文原创内容,转载请标明出处。

原文链接:https://blog.csdn.net/Cixil/article/details/89422200

Verilog的表示形式

Verilog中整数,整型常量即整常数有以下4种进制表示形式:

1)二进制(b或B);

2)十进制(d或D);

3)十六进制(h或H);

4)八进制(o或O)。

数字表达式分为三种:

1)<位宽><进制><数字>,这是最完整的形式。(要求数字格式必须和进制一致,否则编译会出现错误)

2)<进制><数字>,数字的位宽采用默认位宽(不同的机器系统不同,至少32位)。

3)<数字>,采用默认进制(十进制)

位宽

位宽——指的是时间所占位数,而不是指十六进制有几位。前面一个数字代表总共多少bit。然后b,h代表用二进制,十六进制来表示,后面是实际的用多少进制来表示的数据。缺省位宽说明时,一般默认为32位。

**例如:**每一位十六进制数字需要4位二进制数字表示,所以2位十六进制的位宽为8,8’h11等价8’b0001_0001

示例(正确和错误使用)

(1)4’h1,一共4位二进制数。每个数字表示1位十六进制的,即4位二进制数,它表示二进制的4’b0001。

(2)16’h4012,一共16位二进制数。每个数字表示1位十六进制数,即4位二进制数,一共4个数字,所以一共是4*4=16位,他表示二进制的0100_0000_0001_0010。

(3)实际数据值按照写定的位宽进行取舍,只取从最低位数起的4位,其余补零

**(错误示例1)**如4’h1234,

预期为0001_0010_0011_0100,

实际为0100.赋值时根据左值的位宽进行拓展或缩减

4’h1111实际表示4’b0001

16’h1111实际表示16’h1111,即16’b0001_0001_0001_0001;

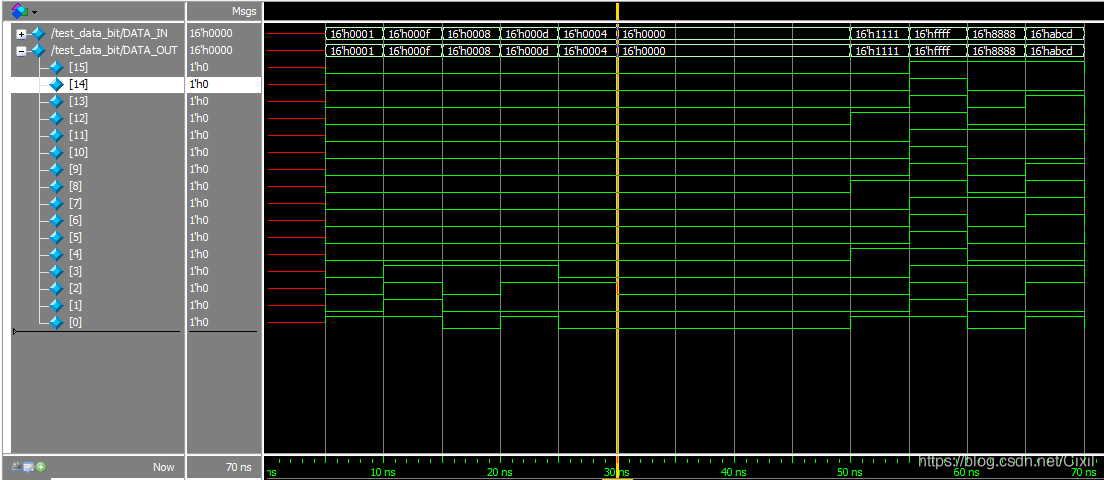

**影响:**位宽不符合时会引起输入输出信号与预期不一致,事实上,若数据与定义位宽不符合,modelsim编译时会出现warning:edundant digits in numeric literal.

**(错误示例2)**如4’b5,

编译错误: Illegal digit for specified base in numeric constant.

附Verilog程序和modelsim仿真结果

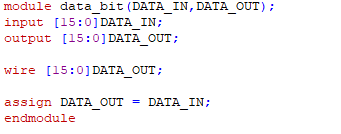

source code

testbench

compile information:(warning:edundant digits in numeric literal.)

simulate result:

代码

源码

//source code

module data_bit(DATA_IN,DATA_OUT);

input [15:0]DATA_IN;

output [15:0]DATA_OUT;

wire [15:0]DATA_OUT;

assign DATA_OUT = DATA_IN;

endmodule

测试文件代码

//test bench

`timescale 1ns/1ns

module test_data_bit;

reg [15:0]DATA_IN;

wire [15:0]DATA_OUT;

initial

begin

#5 DATA_IN = 4'h1111;

#5 DATA_IN = 4'hffff;

#5 DATA_IN = 4'h8888;

#5 DATA_IN = 4'habcd;

#5 DATA_IN = 4'h1234;

#5 DATA_IN = 0;

#20 DATA_IN = 16'h1111;

#5 DATA_IN = 16'hffff;

#5 DATA_IN = 16'h8888;

#5 DATA_IN = 16'habcd;

#5 DATA_IN = 16'h1234;

end

data_bit U1(.DATA_IN(DATA_IN),.DATA_OUT(DATA_OUT));

endmodule

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)