半减器、全减器和减法器原理和设计

半减器、全减器和减法器原理和设计

减法器可由基础的半减器和全减器模块组成,或者基于加法器和控制信号搭建。定义N比特被减数X,减数Y,差为D(difference);来自低比特借位Bi,向高比特借位Bi+1,i为比特序号;所以,有以下结论:

1、半减器

半减器用于计算两比特Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。其真值表、逻辑表达式、Verilog描述和门电路图如下:

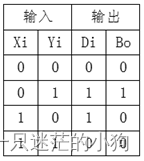

1.1、真值表

1.2、逻辑表达式

xor表示异或。

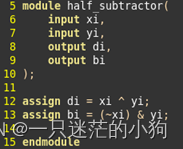

1.3、Verilog设计

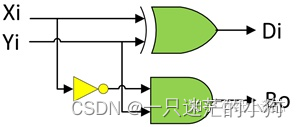

1.4、门电路图

2、全减器

全减器不同于半减器在于,全减器输入来自低位的借位Bi(Borrow input),另外两个输入Xi,Yi,输出为Di和向高位的借位Bo。其真值表、逻辑表达式、Verilog描述和门电路图如下:

2.1、真值表

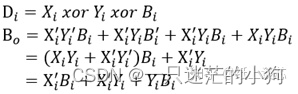

2.2、逻辑表达式

2.3、Verilog设计

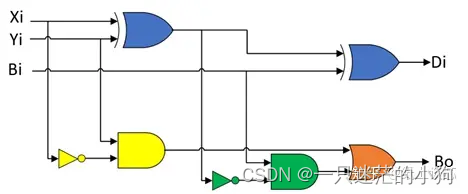

2.4、门电路图

三、减法器

此前,我们介绍了相当数量的加法器设计,而减法器与加法器具有相同的设计方法。用如下符合表示全减器:

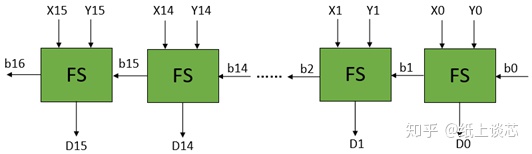

根据此全减器搭建16比特减法器,如下图所示,姑且称之为行波借位减法器。

“行波借位减法器”

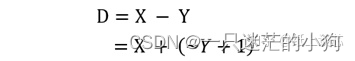

除了使用半减器和全减器搭建减法器外,减法器使用控制信号便可以与加法器共用相同的结构。X与Y均采用二进制补码表示,则:

其中~Y表示对Y按比特取反。

加减法器

以上是基于行波进位加法器修改的电路结构,使其同时具有加法和减法的功能。由加或者减的控制信号,决定该部件的功能。输入c0=0时表示加法;c0=1时表示减法。为了溢出与符号位考虑,以上结构最后进位输出需要与控制信号进行异或以满足减法器的需求。比如0-0的情况。

以下两条RISC-V算术指令:ADD和SUB

ADD rd, rs1, rs2

SUB rd, rs1, rs2

处理器根据指令译码,判断ADD或者SUB,来共用加法减法单元。

四、Verilog设计

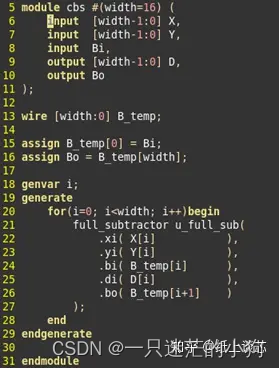

设计一个16比特的减法器

(1)基于全减器设计“行波借位减法器”,基础的全减器模块

加减法器

(2)根据行波进位加法器,通过控制信号,使其同时具有加法和减法的功能,注意进位。

更多推荐

已为社区贡献8条内容

已为社区贡献8条内容

所有评论(0)