数电课设数字钟设计(基于quartus)

数字钟是一种利用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。数字钟的综合性较强,将数字钟作为数电实验大作业的选题不仅可以加深对数电相关理论知识如计数器、组合逻辑电路及时序逻辑电路的理解,还可以有效锻炼工程实践能力。该数字钟以时间显示为基础,在此基础上添加校时及秒表功能,利用Quartus软件设计电路,使用远程平台下载验证。一、方

前言

数字钟是一种利用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。数字钟的综合性较强,将数字钟作为数电实验大作业的选题不仅可以加深对数电相关理论知识如计数器、组合逻辑电路及时序逻辑电路的理解,还可以有效锻炼工程实践能力。该数字钟以时间显示为基础,在此基础上添加校时及秒表功能,利用Quartus软件设计电路,使用远程平台下载验证。

一、方案设计

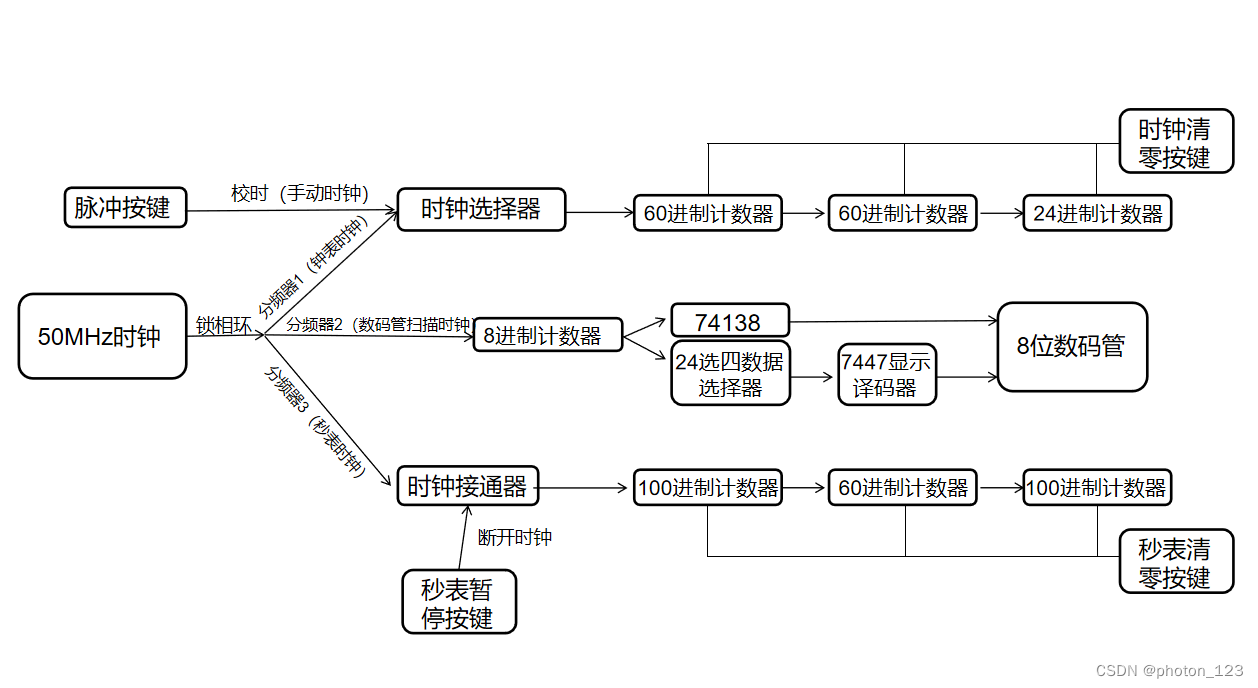

该系统使用74160构建基础计数模块,通过计数器模块的级联实现时分秒的计时,实验平台上的50MHz分频后的1Hz信号作为钟表时钟来源,通过数据选择器与扫描模式来实现多位数码管的显示。系统框图如下:

二、各模块具体设计

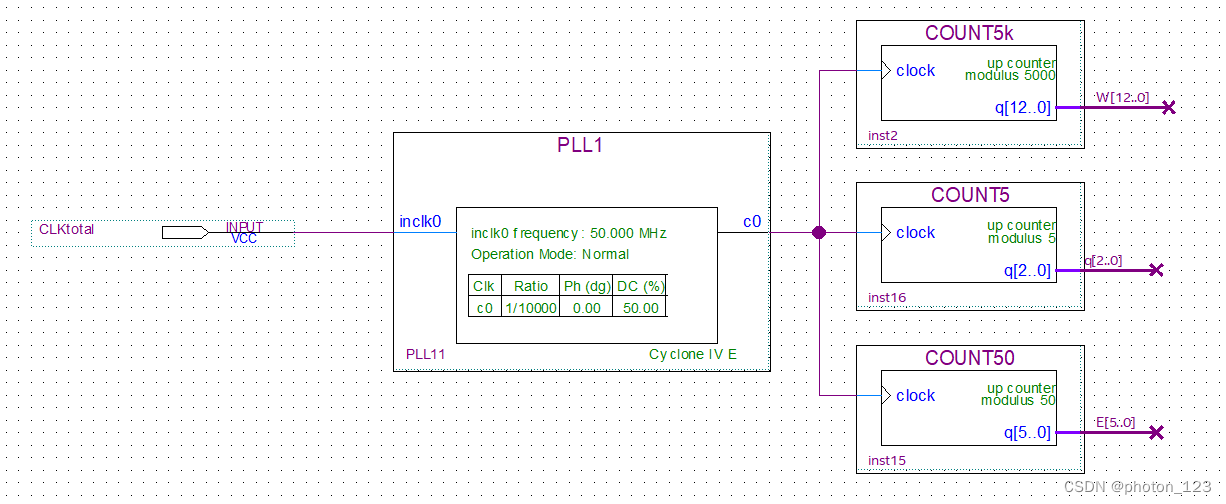

1.分频模块

分频模块将实验平台的50MHz时钟分别转换为1Hz、1000Hz、100Hz分别用于时钟计时、数码管扫描显示及秒表计时。采用锁相环加分频器的宏模块实现,相较于只使用分频器,信号更加稳定。

2.计数器模块

计数器模块使用74160级联而成,采用整体反馈置数法,以60进制计数器为例,将59作为置数反馈信号,低位片为9,高位片为5,同时增加了清零信号以用于时钟的清零,24进制与100进制同理。

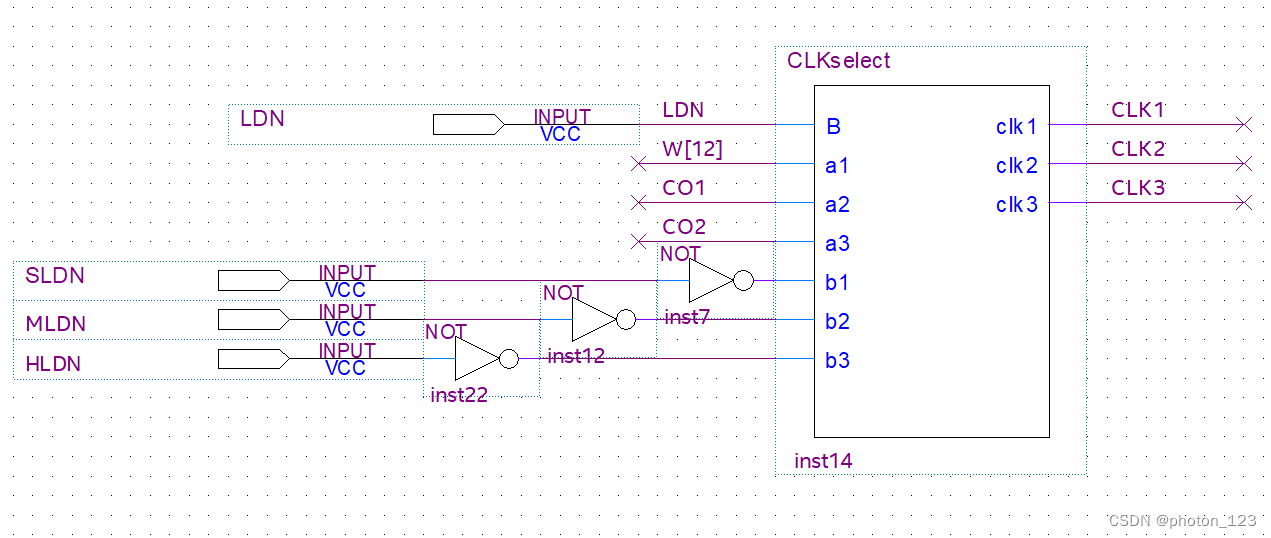

3.校时模块

校时模块使用Verilog代码完成,如下图所示,B为控制信号,B为0时时分秒计数器的时钟信号分别接到默认时钟即上一位的进位信号或分频器的时钟上,B为1时分别接到对应置数信号即按键上,用手动时钟即可实现校时的功能。

module CLKselect(B,a1,a2,a3,b1,b2,b3,clk1,clk2,clk3);

input B,a1,a2,a3,b1,b2,b3;

output clk1,clk2,clk3;

reg clk1,clk2,clk3;

always @(B,a1,a2,a3,b1,b2,b3)

case (B)

1'b0:begin clk1<=a1;clk2<=a2;clk3<=a3;end

1'b1:begin clk1<=b1;clk2<=b2;clk3<=b3;end

endcase

endmodule

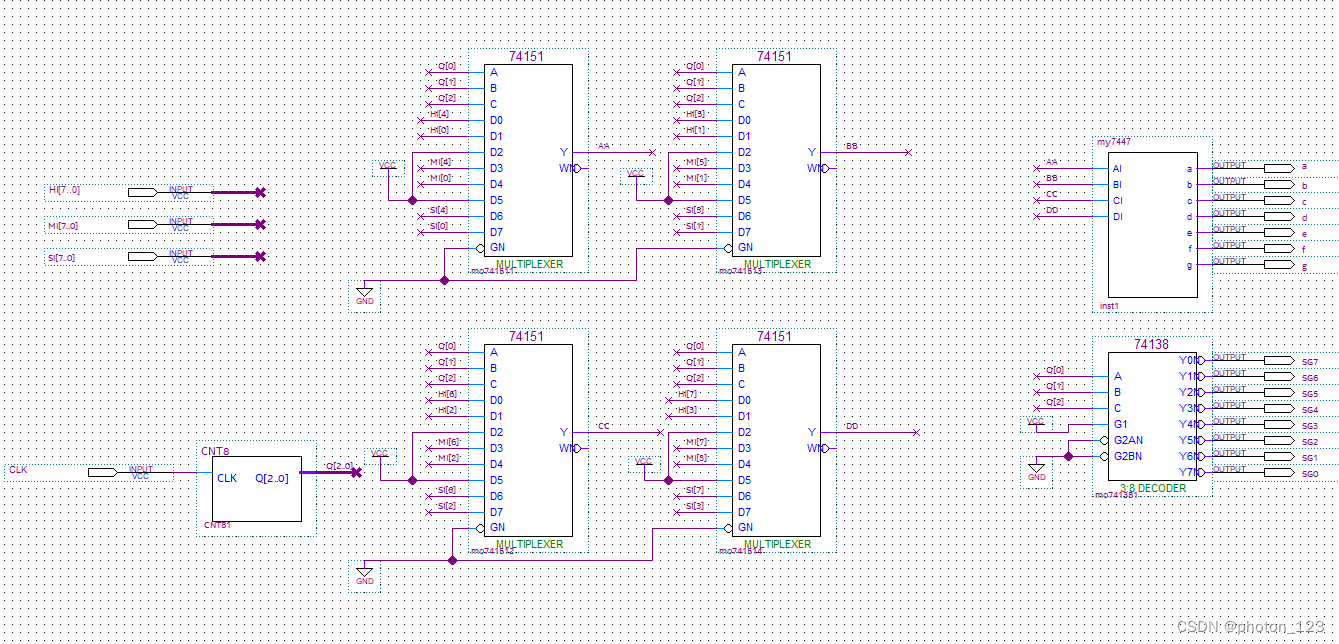

4.数码管显示模块

该模块由8进制计数器、四块74151数据选择器和两块译码器构成,8进制计数器的时钟信号为1000Hz,即为数码管的扫描频率,在八进制计数器的输出信号在0~7循环时,四块74151分别选出小时计数器、分钟计数器、秒钟计数器的高四位和低四位数据,以1000Hz的频率按顺序分别送到显示译码器,在与74138译码器的配合下实现扫描的效果。

为了可以在数码管上显示“-”,将7447进行改造,代码如下,输入译码器的数据不是0~9时只点亮数码管的g段,该数据的产生通过上图中将74151的对应引脚接vcc来实现,这样到对应时刻时4块74151选出的数据是1111即十进制的15,不是0~9的数据,即可显示“-”。

module my7447(AI,BI,CI,DI,a,b,c,d,e,f,g);

input AI,BI,CI,DI;

output a,b,c,d,e,f,g;

reg a,b,c,d,e,f,g;

always @ (AI,BI,CI,DI)

case ({DI,CI,BI,AI})

4'b0000:{a,b,c,d,e,f,g}<=7'b0000001;

4'b0001:{a,b,c,d,e,f,g}<=7'b1001111;

4'b0010:{a,b,c,d,e,f,g}<=7'b0010010;

4'b0011:{a,b,c,d,e,f,g}<=7'b0000110;

4'b0100:{a,b,c,d,e,f,g}<=7'b1001100;

4'b0101:{a,b,c,d,e,f,g}<=7'b0100100;

4'b0110:{a,b,c,d,e,f,g}<=7'b0100000;

4'b0111:{a,b,c,d,e,f,g}<=7'b0001111;

4'b1000:{a,b,c,d,e,f,g}<=7'b0000000;

4'b1001:{a,b,c,d,e,f,g}<=7'b0000100;

default {a,b,c,d,e,f,g}<=7'b1111110;

endcase

endmodule

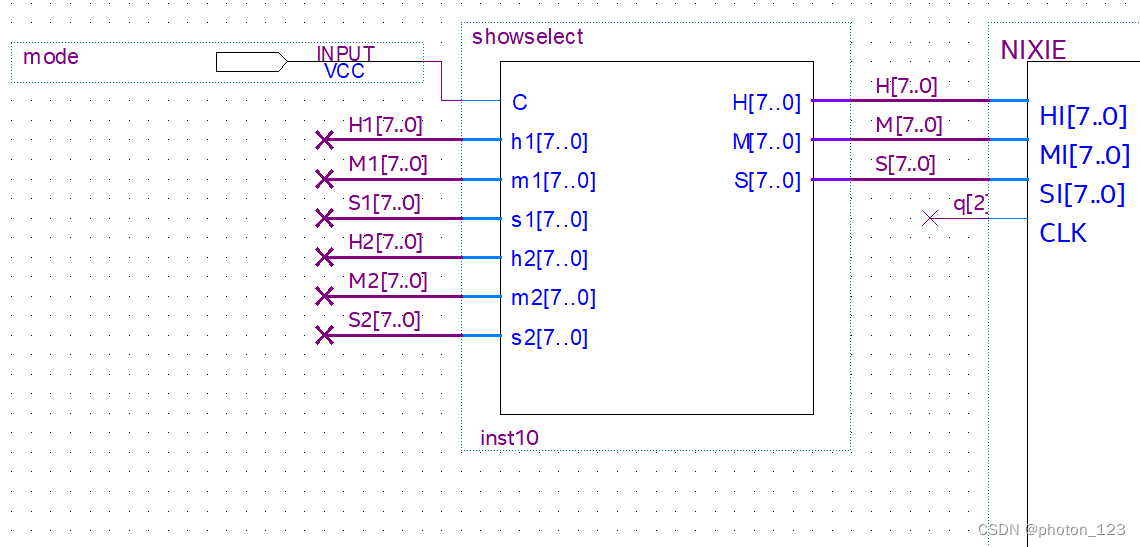

5.模式选择模块

该模块的本质是数码管显示的切换,采用Verilog代码实现,C为控制信号,C为0时将输出信号接到钟表的时分秒计数器的输出总线上,C为1时将输出信号接到秒表的三个计数器的输出总线上,最后再将该模块的输出信号接到数码管显示模块的输入上,即可通过改变控制信号来实现钟表模式和秒表模式的切换。

module showselect(C,h1,m1,s1,h2,m2,s2,H,M,S);

input [7:0]h1,m1,s1,h2,m2,s2;

input C;

output [7:0]H,M,S;

reg [7:0]H,M,S;

always @(h1,m1,s1,h2,m2,s2)

case(C)

1'b0:begin H<=h1;M<=m1;S<=s1;end

1'b1:begin H<=h2;M<=m2;S<=s2;end

endcase

endmodule

6.秒表暂停模块

该模块也使用代码完成,D为控制信号,D为0时接通秒表时钟,D为1时输出为0即断开秒表时钟,实现秒表暂停的功能。

module secwatchstop(D,clk,S);

input D,clk;

output S;

reg S;

always @(D,clk)

case (D)

1'b0:S<=clk;

1'b1:S<=1'b0;

endcase

endmodule

三.设计过程中出现的问题及解决方法

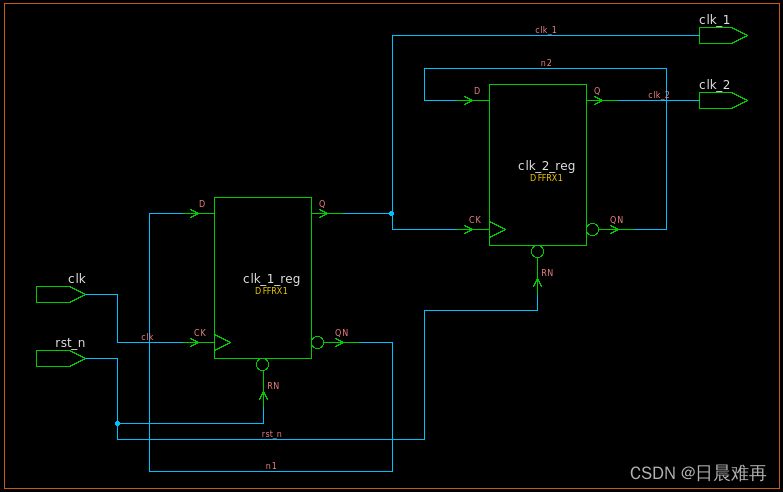

1.校时控制信号恢复时,时分秒三个计数器的值会加1。经分析,该问题产生的原因是在校时控制信号的按键恢复的瞬间将时钟信号从手动时钟切换为默认时钟时产生了一个上升沿,导致三个计数器的值都加1。解决方法是将校时模块手动时钟信号的输入上都添加非门,这样即使按键恢复的瞬间也不会产生上升沿。

2.时钟的计数器在59就产生进位而不是00时再产生。经分析,导致该问题的原因是进位信号的上升沿提前一秒到来,解决方法是在计数器模块的进位信号不加非门,这样进位时进位信号由1变为0,持续一秒之后即59到00转换的瞬间由0恢复为1,产生一个上升沿,将上升沿的信号推迟了一秒。

该工程所有文件的百度网盘链接:

链接:https://pan.baidu.com/s/1x3Rql6J5tCNwfcfs3YsXAw

提取码:8421

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)