DCDC芯片内部模块原理

DCDC芯片内部模块原理1.概述1.1 芯片的生产过程1.2 前言2.内部框图参考文献1.概述1.1 芯片的生产过程1)沙子到晶圆:沙子经过化学反应变成多晶硅然后再经过化学反应变成单晶硅,一般是硅晶柱,然后经过切割抛光后变成硅晶圆。一般说的8寸、12寸指的是晶圆的直径。2)光刻:在硅片上涂上光刻胶,紫外线通过掩膜照射在光刻胶上,掩膜上有通过VHDL/verilog综合后生成的电路图,被照射的光刻胶

DCDC芯片内部模块原理

1.概述

1.1 芯片的生产过程

1)沙子到晶圆:沙子经过化学反应变成多晶硅然后再经过化学反应变成单晶硅,一般是硅晶柱,然后经过切割抛光后变成硅晶圆。一般说的8寸、12寸指的是晶圆的直径。

2)光刻:在硅片上涂上光刻胶,紫外线通过掩膜照射在光刻胶上,掩膜上有通过VHDL/verilog综合后生成的电路图,被照射的光刻胶溶解,经过蚀刻,晶圆上留下跟掩膜一样的电路。

3)掺杂:加入其他杂质形成晶体管,加入铜与其他晶体管相连,然后重复2),一般芯片大概需要有几十层。

4)封装:经过上面简介的步骤后,晶圆上有很多裸芯,将裸芯切割,加上键合线后,加上外壳就形成成品芯片了。

1.2 前言

之前涉及的电源都是分立器件搭建的,很想了解下一颗电源芯片内部构造和原理,于是开始这篇博文。

2.内部框图

DCDC芯片以buck芯片为例进行说明。内部包括的模块有基准电压电路、自举电路、误差比较电路、电流检测电路、欠压保护电路、软启动电路、过温保护电路等。

下面是一款电流控制型buck芯片tps54620。

上图放在这里主要方便看芯片内部有哪些东西,当然有些功能模块还没画出来,下面的介绍按照个人想了解的部分说明。

3.各部分基本原理

3.1 带隙基准

首先说明的是什么是带隙?

带隙是导带的最低点和价带的最高点的能量之差。

价带:价电子占据的能带。价电子指的是已键合的电子,通常存在半导体和绝缘体中。

导带:自由电子存在的能量带。

叫带隙基准的原因是与硅的带隙电压差不多。

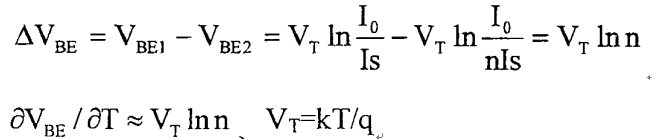

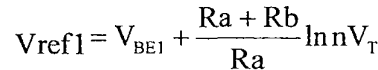

带隙基准:由正温度系数和负温度系数的电路组成的基准电压,不受电压和温度的影响。主要是为其他电路提供稳定精确的参考源。

正温度系数电路:由单个BJT组成的电路,其Vbe与温度负相关。

负温度系数电路:两/多个BJT相减组成的电路,负负得正。

将正温度系数电路跟负温度系数进行加权求和即可得到与温度变化无关的电路,加权求和通过运放组成的加法电路实现。

电阻值和BJT的个数选取保证这个等式与温度无关即可.

另外由于电阻和设计不精确性,还采用trimming电路进行修调,一般采用熔丝微调,通过熔断熔丝,来改变电阻值,从而保证基准电压的稳定。

以上讲的主要是基本原理,具体在设计中比较麻烦,运放的实现、差分电路、加/减法电路等都需要用BJT/MOS搭建出来,很复杂,对模电要求高,有时间可具体分析里面的原理。

3.2 软启动电路

软启动的作用是避免输入浪涌电流大,导致输出过冲,基本思想是,在启动初期将开关管的导通时间从小慢慢放大,直至正常。

根据下图来介绍基本原理。SS引脚与地之前的电容控制了软启时间,上电时,VBIAS通过电流源给电容充电,SS端获得一个缓慢抬升的信号,此信号作为误差放大器的基准电压,VSENSE是反馈电压,上电时为0,这样误差放大器的输出很小,开关管的导通时间就很小,直到ss电压达到正常基准电压值并被接管,后SS被电流源充电到一定的电压值。

3.3 电流检测

Rs是电流采样电阻,跟分立器件搭建电源的电流采样方法基本类似。

3.4 过温保护

过温保护电路其实还是利用BJT的Vbe受温度的影响实现的。

下图是其中一种典型的过温保护电路,实际中有优化,这里只是说明实现的基本思想。

R2,R3,M9用来改变A点的电压值,A点电压值与Q1的Vbe比较可实现对输出的控制,温度改变就是改变Q1的Vbe的值,温度高Vbe小,Q1容易导通,这里来通过M9形成了正反馈,斯密特触发器保证温度超过一定值时,Vout跳变,输出高电平,后续再关断控制管,当温度低于一定值时,恢复。

3.5 过流/过压/欠压保护

主要是利用迟滞比较器设置门槛电压电流值,来控制功率mos的导通和关断。有的过流控制通过检测mos导通时的电压控制,因为电压跟电流成正比,然后通过比较电压再来控制mos驱动。

3.6 频率选择

3.6.1 振荡器

【首先说说最简单的RC正弦振荡电路。

正弦波振荡电路有两个条件:振幅平衡和相位平衡。这要求电路是正反馈,即使输入消失,输出也可以保持,这必然是在特定频率下发生的,所以电路需要选频网络。

RC电路用来选频,C的充放电是决定频率产生的要素。因为直流输入频谱很宽,包括RC选出的频率,信号经过放大后输出,为了维持输出稳定又加入了点负反馈。】(此段跟下面振荡器似乎没有递进关系,仅作为复习。)

张弛充放电振荡器是DCDC芯片中比较常用的振荡器。主要由电流源、RS触发器、电压比较器和mos等组成。下图是基本原理图。

上图中两mos决定了电容C的充放电,电容C的充放电形成了一定频率的锯齿波,比较器决定了电容电压的范围,触发器给mos提供一定频率的驱动,电流源的大小可控制振荡频率(CU=It),当然也需要正反馈维持输出的振荡。

3.6.2 外同步的振荡器SYNC

有些dcdc芯片有sync这个引脚,来看看这个引脚的功能实现方式。外同步的作用是为了消除多个电源芯片串并联引起的差频,这种差频对电源稳定性和纹波有影响。

外同步主要是在张弛充放电振荡器上叠加了在电容电压未达到高门槛VH+时的外部同步信号,使其提前放电,与sync同步,另外增加了one-shot整型电路用来减小sync的脉宽给RS触发器识别。这种方式决定了sync的外接频率高于内部晶振的频率。

当SYNC作为输出引脚时,有个180°异相同步的概念。

180°异相同步就是说,两DCDC共用一个输入时,为减小输入电流纹波,将时钟控制信号做成同频率但相差180°相位,即时钟互补,这样输入电流的纹波则可叠加减小。这类似于三相整流纹波小于单相整流的。

3.6.3 频率控制

dcdc芯片中一般有RT引脚,改变RT引脚与地之间的电阻即可改变DCDC的频率。改变RT的电阻,其实是通过改变电容充电恒流源的大小改变振荡器的频率。

3.7 EN使能电路

EN使能电路的基本原理是基于斯密特触发器。

首先简单回顾下斯密特触发器的原理。

下图是同相斯密特触发器,反馈为正反馈,正反馈可保证输出电压到门限值。

当Vi大于Vt1是,输出为高门限,当小于Vt2时,为低门限。设置好电阻比例以及输出门限值,即可得到输入门限电压。当然最终芯片里的设计可能如下图,用mos管搭建。

EN的门限为其他模块提供全局使能信号。

4.总结

在测试芯片时,内部原理一直没有探究,最近终于打开了这个盲盒,相信对以后dcdc芯片测试有更深的理解。

芯片内部结构看似复杂,其实用到的基本模块很少,涉及门限的比如EN,ULVO,OC等一般用到了迟滞比较器(斯密特触发器);涉及温度的如带隙基准,过温保护,其实是利用BJT/mos的温度特性;涉及到电压稳定的用到了运放,包括正/负反馈;涉及到频率或者软起,用到了电容的充放电。

集成电路再打碎一点,全部都是用mos/BJT实现的,无论是运放,逻辑电路,电流源等,所以学好模电是很重要的,这样想来大学时的教学安排还是挺牛的,数模电永远是经典。

参考文献

《BUCK型DC_DC开关电源芯片的设计与实现》

《电流模式DCDC降压稳压器芯片的研究与设计》

《D-CAP模式控制的Buck型DC-DC的研究与设计》

《BUCK型DC-DC中关键电路的研究与设计》

《带外同步功能的高效降压型DC-DC芯片的研究》

《开关型降压DC-DC转换器设计》

《一种异相双输出同步整流BUCK型DC-DC控制器设计与研究》

《电子技术基础模拟部分(康华光)》

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)