版图基本知识

版图层次定义层英文(缩写)版图层有源区Active (diff / thin oxide)TON阱NwellTB场注入—PT正常Vth沟道注入—BC低Vth NMOS沟道注入LVN低Vth PMOS沟道注入LVPPS耗尽型NMOS沟道注入VDNND耗尽型PMOS沟道注入VDPPD纵向NPN基区注入P-baseBA多晶硅Poly1GTN型源/漏N+SNP型源/漏P+SP

一键AI生成摘要,助你高效阅读

问答

·

版图基本知识

版图层次定义

| 层 | 英文(缩写) | 版图层 |

|---|---|---|

| 有源区 | Active (diff / thin oxide) | TO |

| N阱 | Nwell | TB |

| 场注入 | — | PT |

| 正常Vth沟道注入 | — | BC |

| 低Vth NMOS沟道注入 | LVN | |

| 低Vth PMOS沟道注入 | LVP | PS |

| 耗尽型NMOS沟道注入 | VDN | ND |

| 耗尽型PMOS沟道注入 | VDP | PD |

| 纵向NPN基区注入 | P-base | BA |

| 多晶硅 | Poly1 | GT |

| N型源/漏 | N+ | SN |

| P型源/漏 | P+ | SP |

| ROM | ROM | RO |

| Poly2阻挡层 | High Res | IM |

| Poly2 | Poly2 | PC |

| 接触孔 | Contact | W1 |

| 金属1 | Metal1 | A1 |

| M1和M2接触孔 | VIA1 | W1 |

| 金属2 | Metal2 | A2 |

| M2和M3接触孔 | VIA2 | W3 |

| 金属3 | Metal3 | A3 |

| 焊盘PAD | PAD | CP |

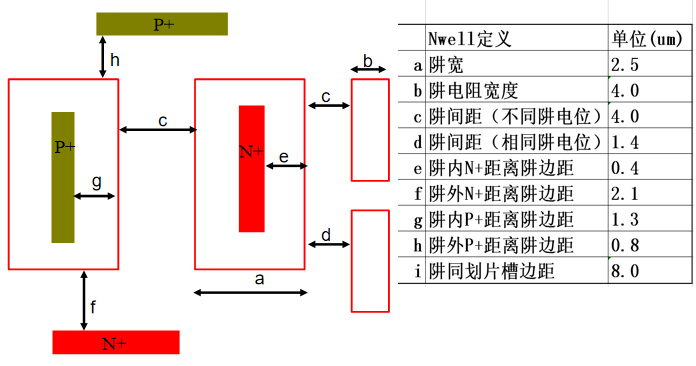

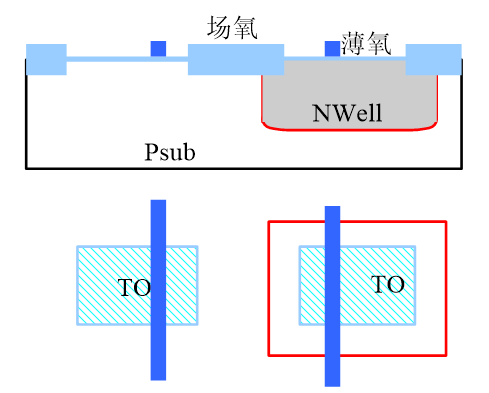

N阱

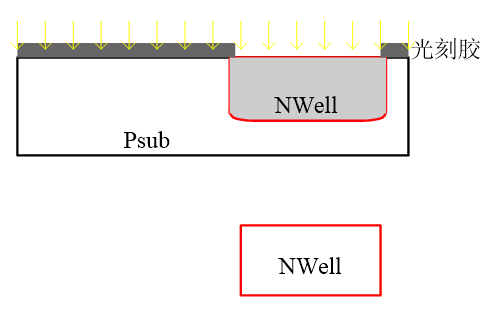

N阱概念

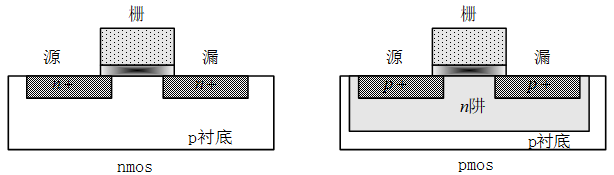

- 如果制造集成电路的硅片掺杂了磷等施主杂质,则该类型的硅片称为n型硅;如果掺杂了硼等受主杂质,则该类型的硅片称为p型硅。

- 在制作CMOS集成电路时,N沟MOSFET(简称NMOS)直接制作在p衬底上;P沟MOSFET(简称PMOS)需要制作在N阱上。

- 实际上制造集成电路前,有些CMOS工艺需要先在硅片上生长一层外延层,以减少闩锁效应的影响。习惯上把外延层和原来的衬底都称作衬底。使用p衬底n阱的工艺称为N阱工艺。使用n衬底p阱的工艺称P阱工艺。

- 现代工艺出于牺牲PMOS性能来优化NMOS性能,所以大多数工艺都是N阱工艺;也有同时使用N阱和P阱的工艺,称为双阱工艺。

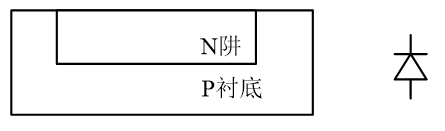

- N阱和P衬底构成寄生二极管,在CMOS电路中衬底通常接最低点评,确保二极管处于反偏。

N阱的作用

- 主要作用制造PMOS;

- 掺杂浓度较低,电阻率较高,可用于制造电阻,称为阱电阻;

- N阱可以和衬底构成二极管,可用于制造寄生PNP管。

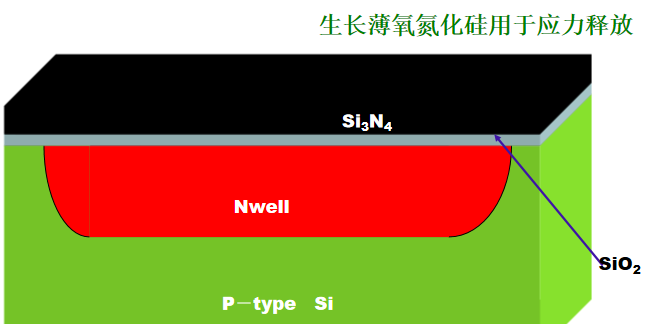

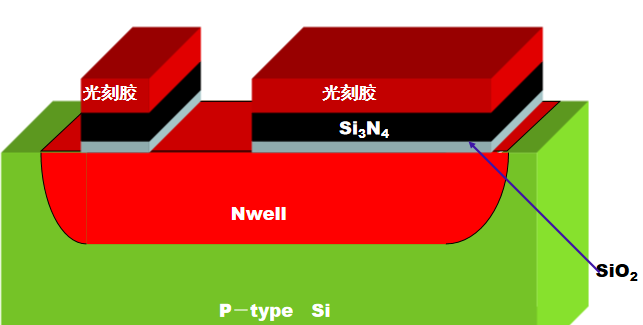

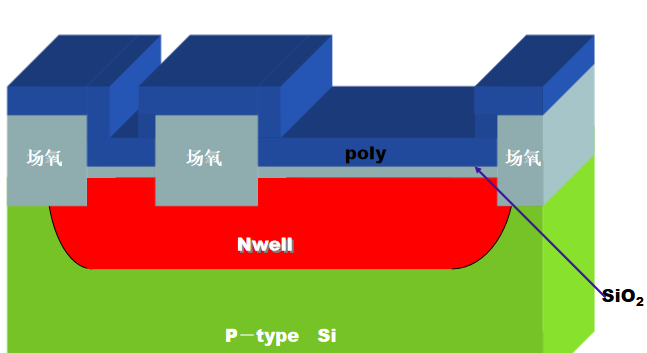

N阱制作

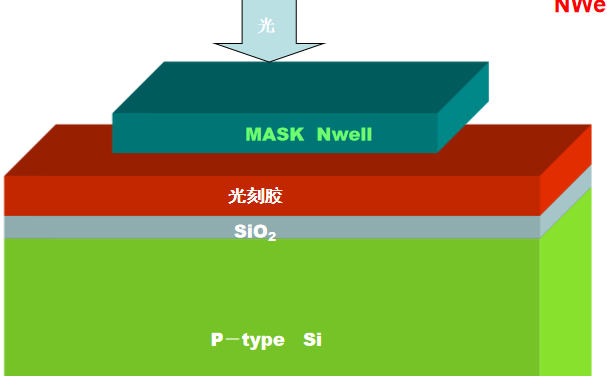

-

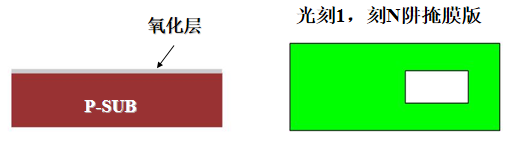

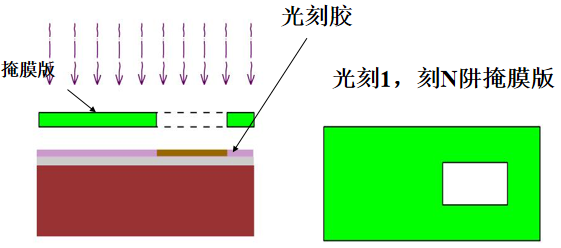

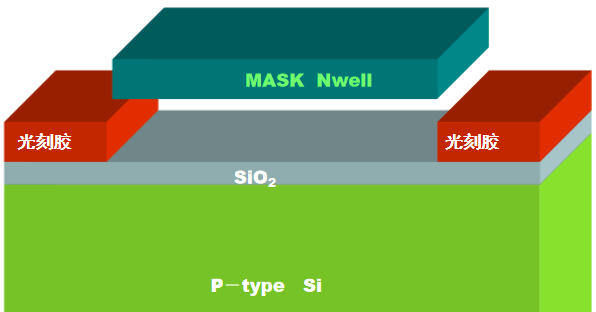

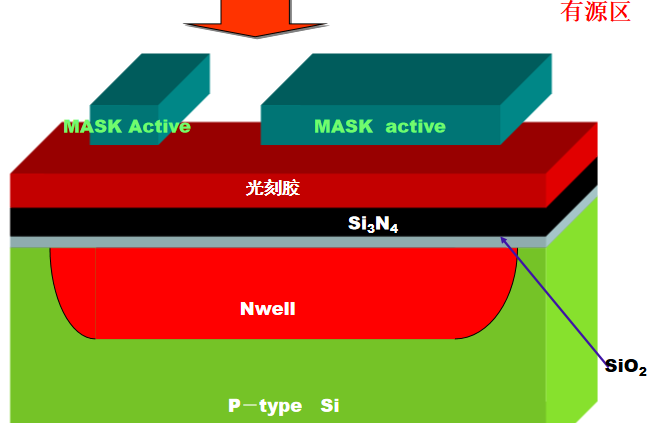

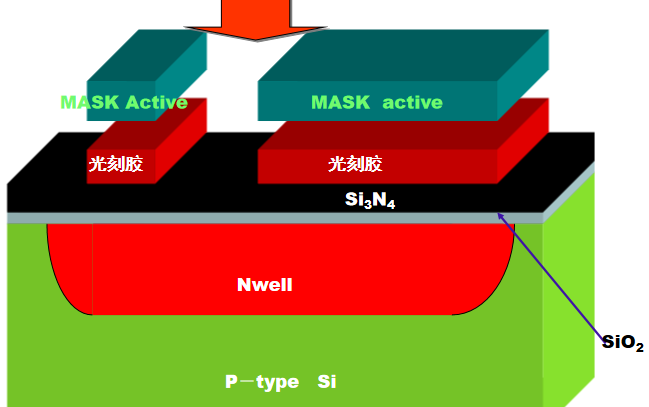

硅片涂胶后,通过N阱掩模版,将硅片放在光线下,通过显影去掉被光照的光刻胶;

-

氧化层生长

-

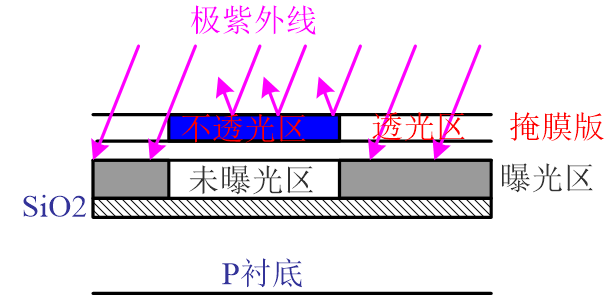

曝光

- 在光刻胶工艺过程中,涂层曝光、显影后,曝光部分被溶解,未曝光部分留下来,该涂层材料为正性光刻胶;

- 此时的掩模版类似遮光板,绿色部分不透光,镂空的白色部分透光;

- 在光刻胶工艺过程中,涂层曝光、显影后,曝光部分被保留下来,而未曝光被溶解,该涂层材料为负性光刻胶。

- 此时的掩模版类似透明板,蓝色部分不透光,其余部分透光;

- 无论是哪种方式,核心思想都是制造一个区域,用以掺杂;

-

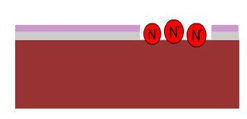

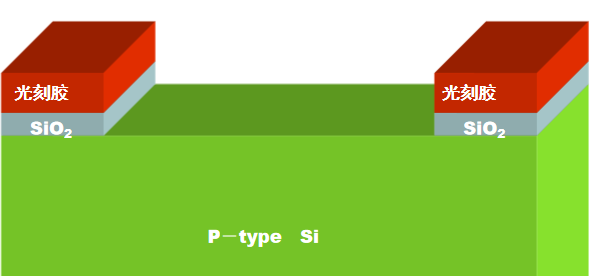

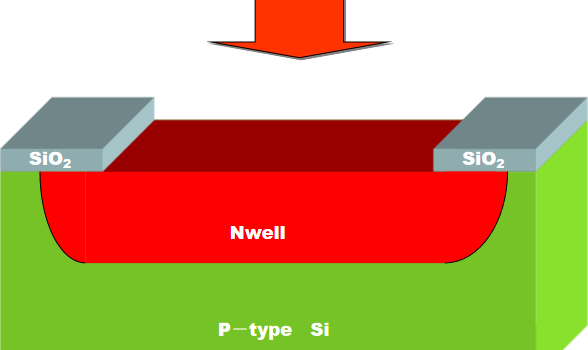

掺杂

- 将硅片暴露在施主原子下,施主杂质会被光刻胶挡住,同时通过光刻胶上的开孔扩散到开孔区域的硅片中;

- 将硅片暴露在施主原子下,施主杂质会被光刻胶挡住,同时通过光刻胶上的开孔扩散到开孔区域的硅片中;

-

去掉光刻胶,形成N阱

- 扩散到一定时间后,N阱的深度达到工艺期望值。

- 施主杂质不仅会沿垂直硅片的方向扩散(纵向扩散),也会在硅片中间向四周扩散(横向扩散),此特性跟N阱的设计规则密切相关。

N阱制作流程图

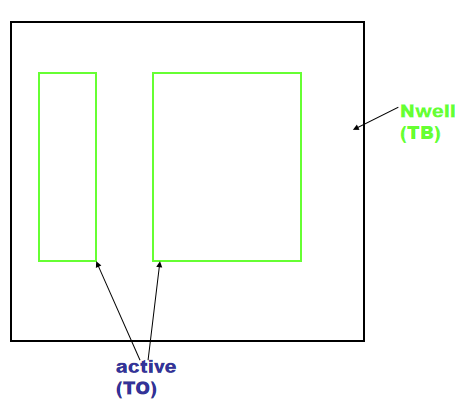

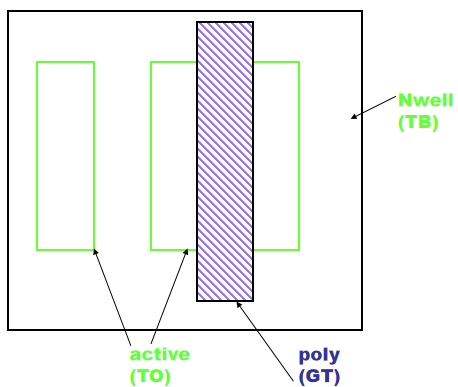

Layout图示

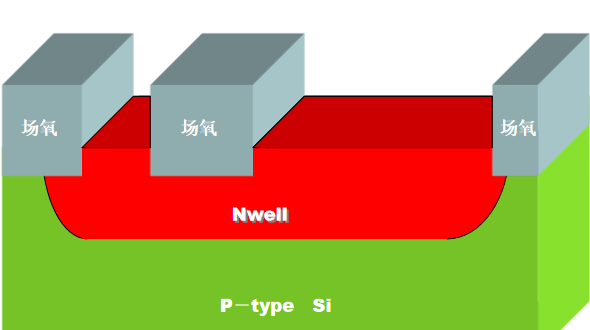

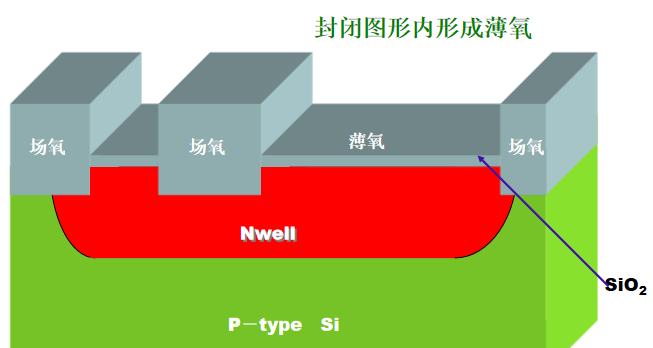

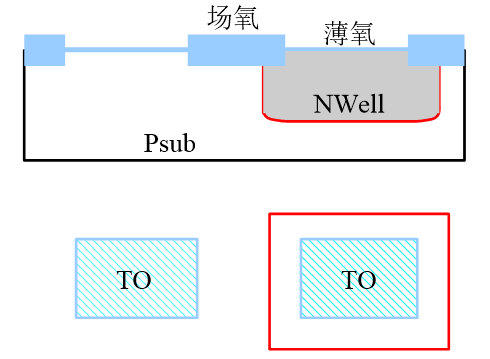

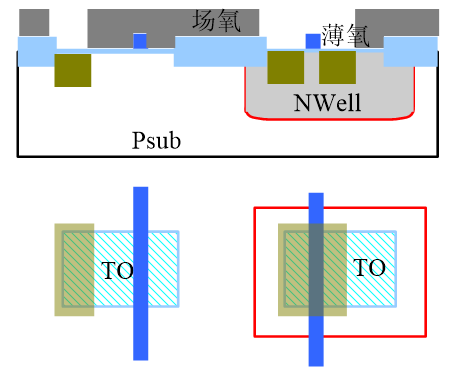

有源区(薄氧区)

有源区概念

- 源区、漏区、沟道区合称MOS管的有源区,有源区之外的区域定义为场氧区(Fox)。有源区跟场氧区之和就是整个芯片表面,即 Active + Fox = Surface。

- 有源区叫Active,也叫diff 或 thin oxide。

- 有源区只要用于制造N型器件和P型器件,也可以用于金属1和衬底或阱的接触。从某种意义上说有源区的掩膜板主要用于打开离子注入的窗口。

- 实际上有源区掩膜板的意义在于作为制造硅局部氧化(LOCOS)和薄氧(封闭图形内形成薄氧,封闭图形外形成LOCOS)。

有源区制造

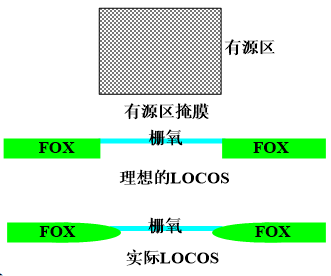

LOCOS

- LOCOS (Local Oxidation of Silicon:硅的局部氧化): CMOS工艺最常用的隔离技术,以氮化硅为掩膜实现了硅的选择氧化,在这种工艺中,除了形成有源晶体管的区域以外,在其它所有重掺杂硅区上均生长一层厚的氧化层,称为隔离或场氧化层。

- 缺点:常规的LOCOS工艺由于有源区方向的场氧侵蚀(SiN边缘形成类似鸟嘴的结构,称为“鸟喙效应”bird beak)和场注入的横向扩散。

- 这种侵蚀会影响MOSFET的沟道宽度,所以实际制造出来的器件的沟道长度会比版图所画的沟道长度小。现代工艺中0.25um以下特征尺寸的工艺一般不使用LOCOS做隔离,而是使用浅槽隔离(STI)。

Layout图示

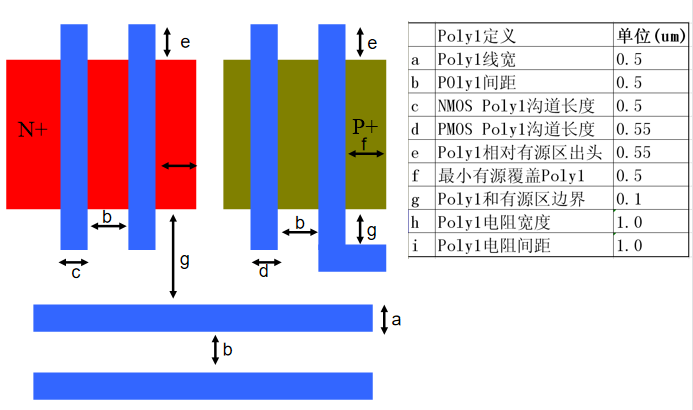

多晶硅1(Poly1)

- 作用

- 最主要的作用是用于制造MOSFET的栅;

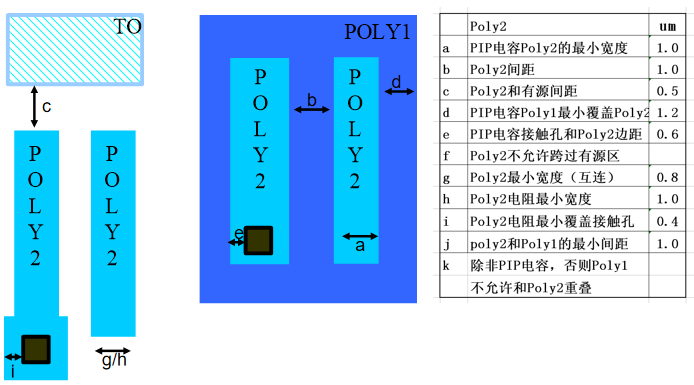

- Poly1和Poly2制造PIP电容(多晶硅1—绝缘层—Poly2);

- Poly电阻;

- Poly互连(此时最大的问题是Poly的方块电阻数量级比较大);

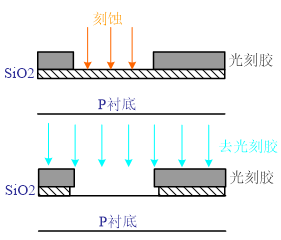

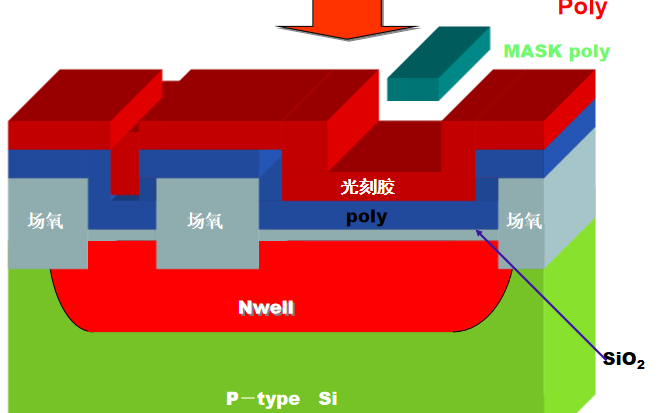

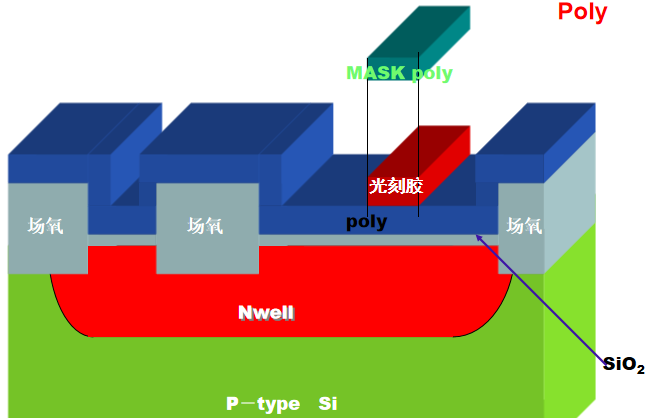

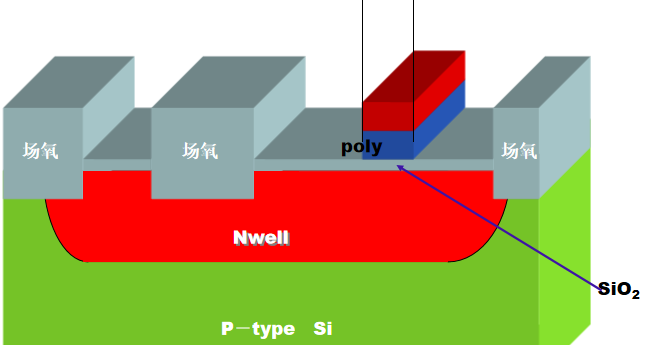

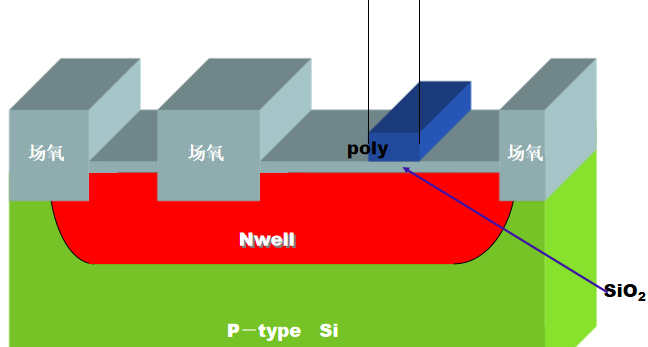

栅极制作

- 晶体管中栅结构的制作是流程中最关键的一步,因为它包含了最薄栅氧化层的热生长以及多晶硅栅的刻蚀,而多晶硅栅的宽度通常都是整个硅片上最关键的线宽。

- 栅氧化层的生长 > 多晶硅淀积 > 多晶硅掩模制作 > 多晶硅栅刻蚀

- Poly跨过有源区时,源、漏和沟道自对准于栅,这也称为自对准工艺。

- 在不制作器件时,禁止多晶跨过有源区,避免产生寄生器件。

- 多晶在形成器件时,需要超过有源区一定距离,保证源漏不会发生短路。

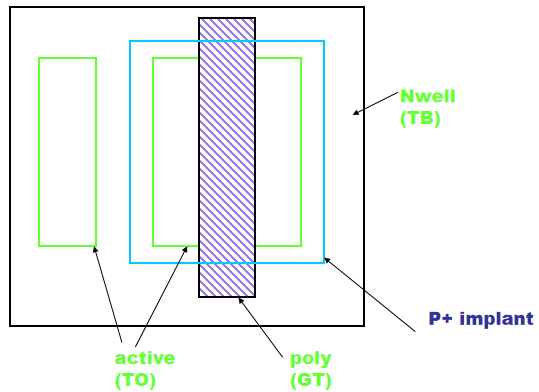

Layout图示

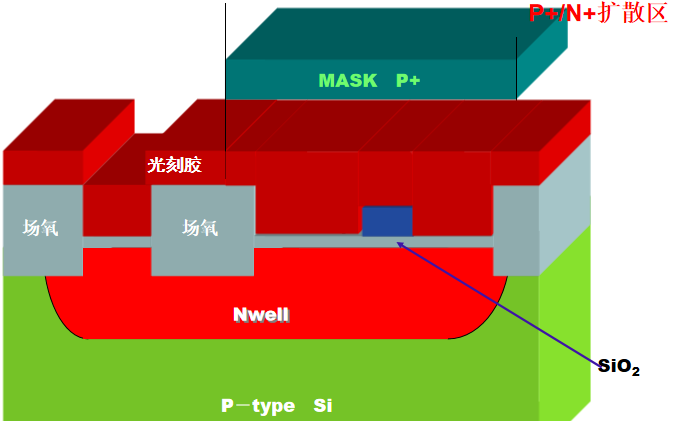

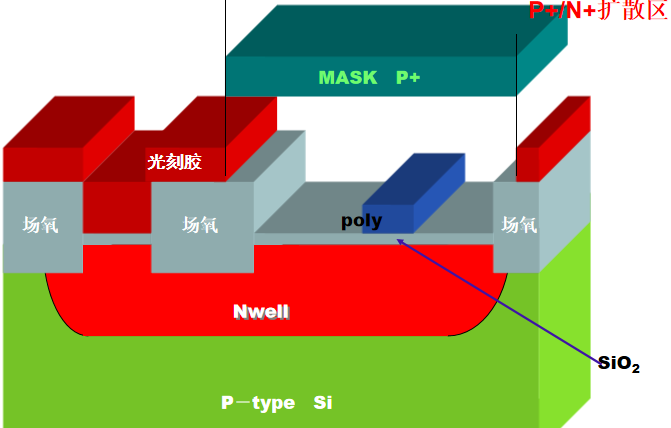

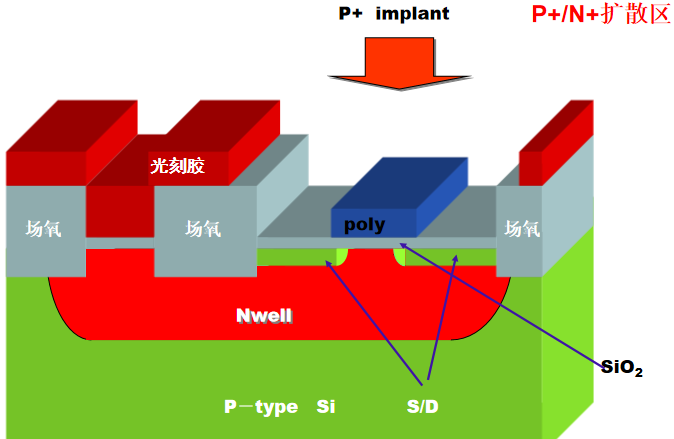

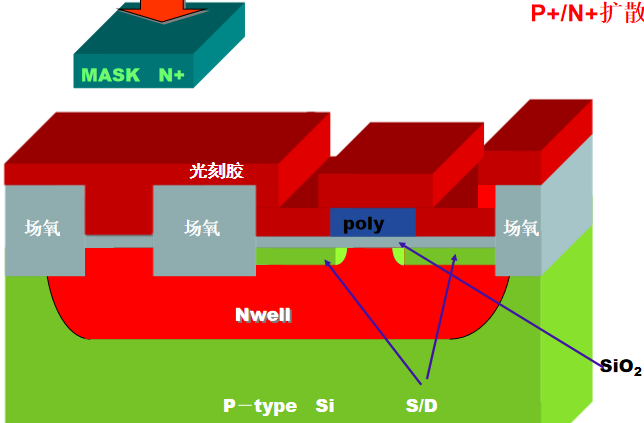

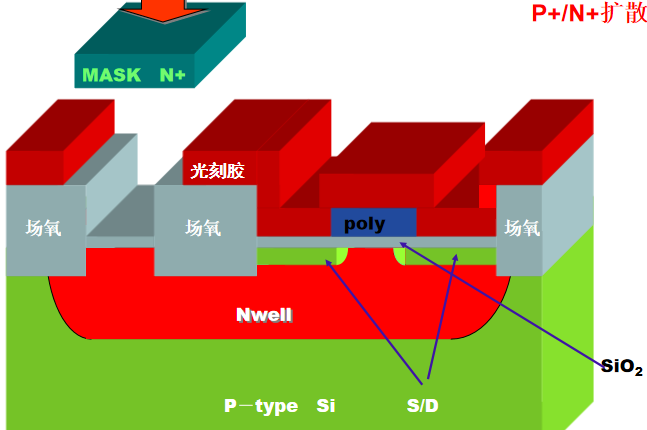

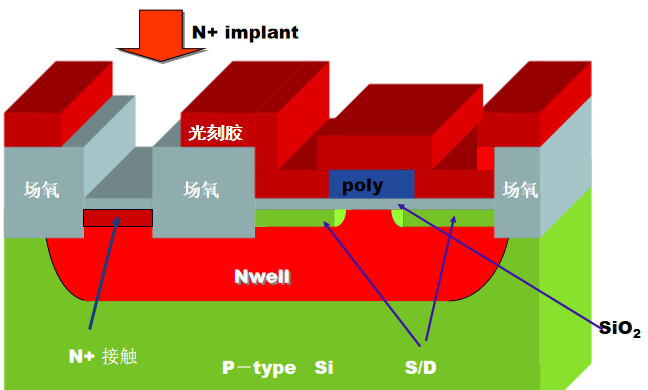

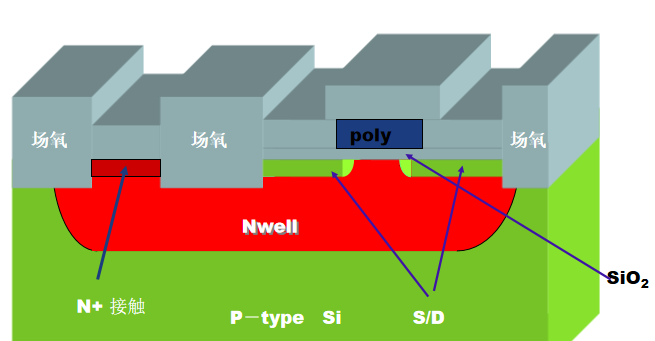

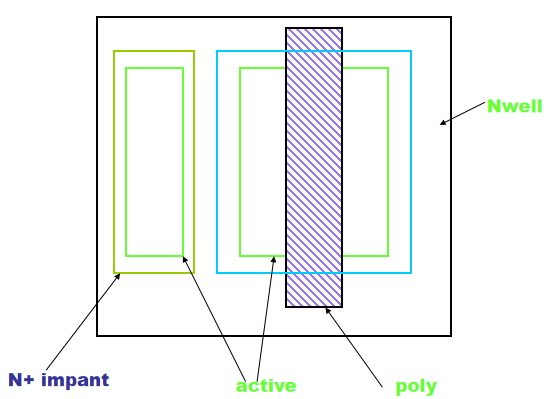

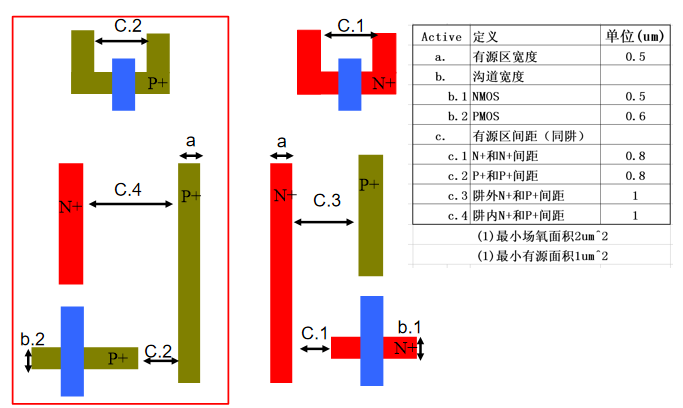

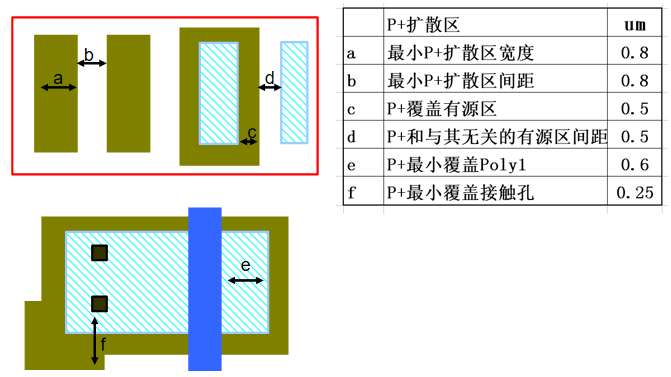

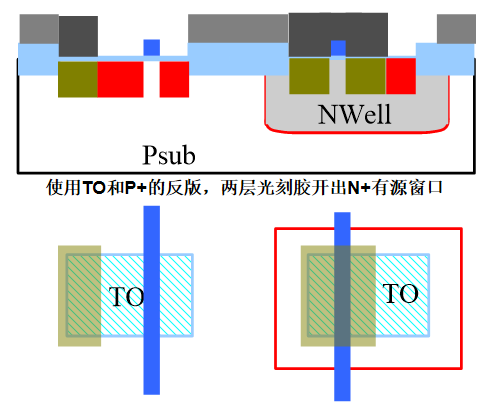

P+/N+扩散区

- 有源区的掩膜板主要用于打开离子注入的窗口。而P+和N+扩散区的作用在于实现离子的注入,从而控制硅的掺杂类型。

- 多晶硅栅可以作为NMOS和PMOS的源/漏的自对准掩膜,注入可以按照任意顺序进行,可以先进行N型源漏的注入,也可以先进行P型源漏的注入。

Layout图示

Layout图示

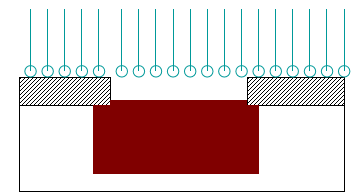

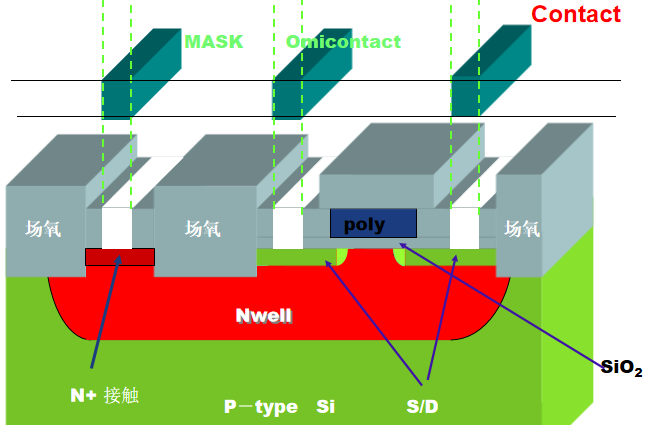

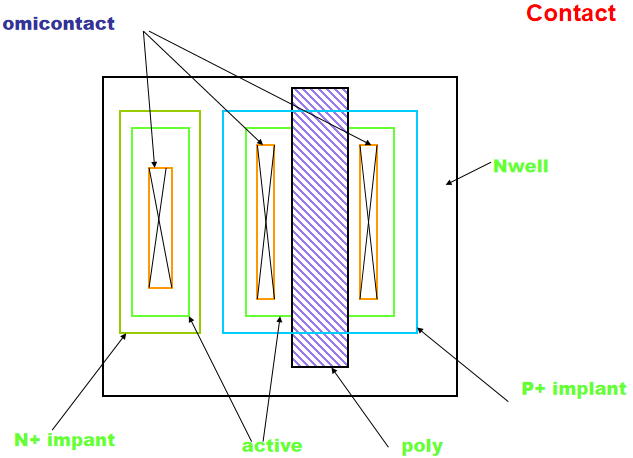

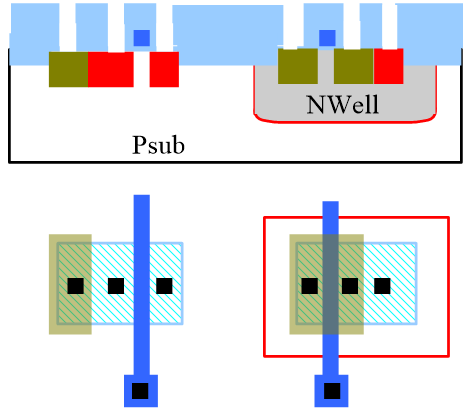

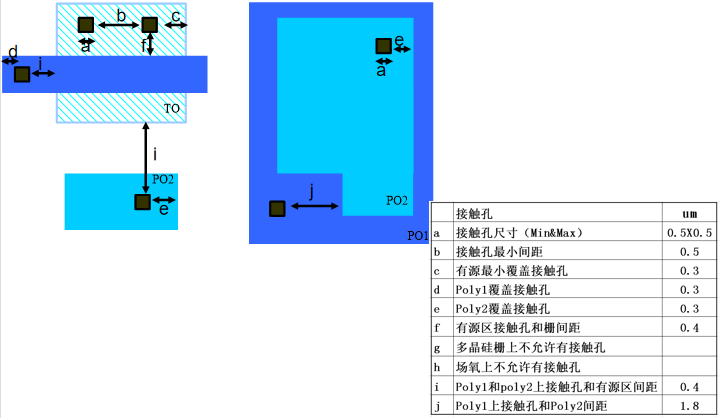

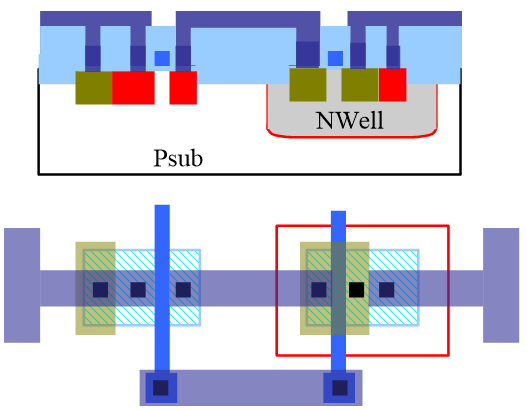

接触孔

- 接触的目的是在所有的硅的有源区和Poly形成金属接触,这层金属接触可以使硅和随后淀积的金属导电材料更加紧密的结合。

Layout图示

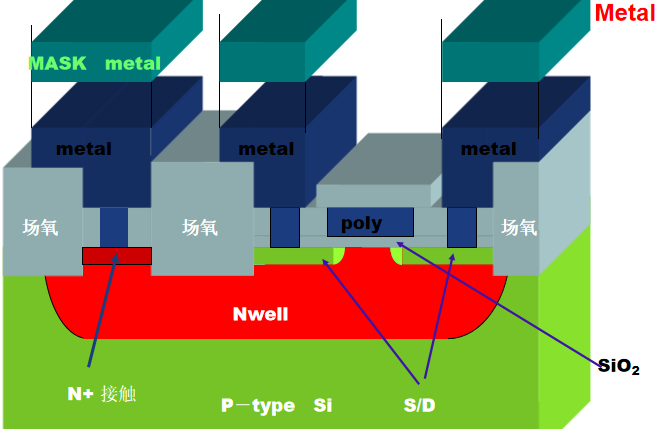

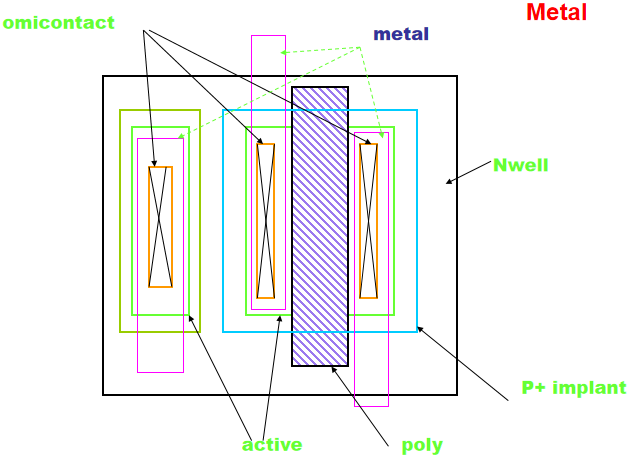

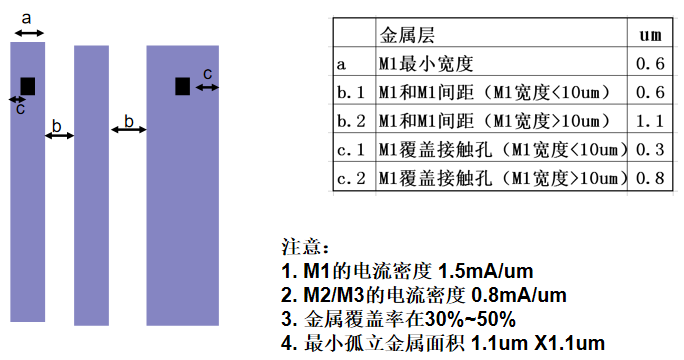

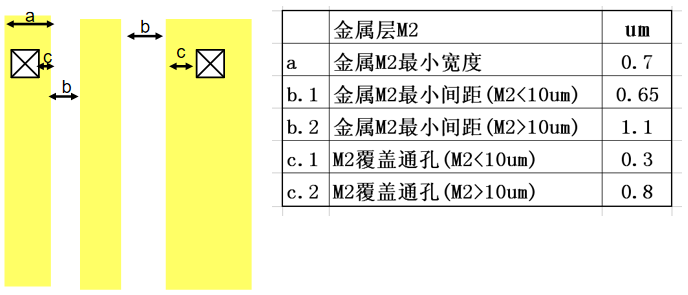

金属层(Metal)

- 接触孔硅化后,在晶圆上淀积掺铜的铝层,淀积金属后的晶圆涂上光刻胶并采用金属掩模版光刻,去除不需要的金属,形成互连结构。

Layout图示

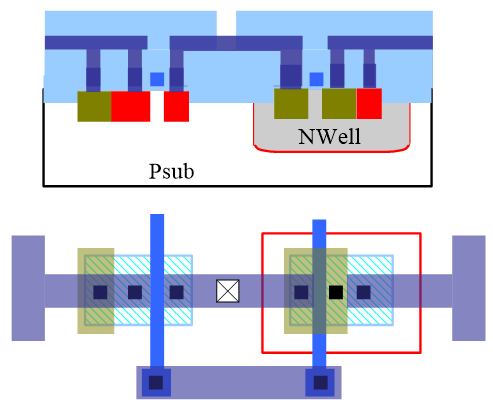

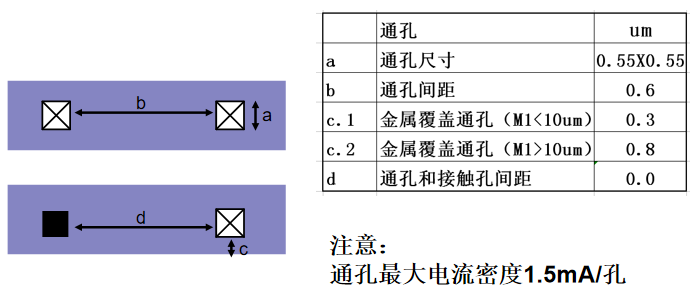

通孔VIA

- 层间介质充当各层金属以及第一层金属与硅之间的介质材料。层间介质上有许多小的通孔,这些层间介质为相邻的金属层之间提供了电学通道。通孔中常用导电金属(比如钨)来填充,形成金属层间的电学通路。

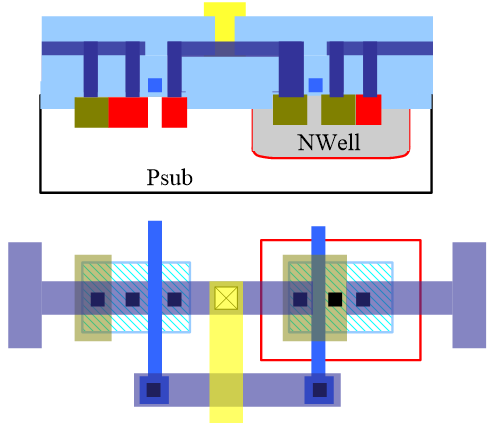

简单反相器版图

N阱(TB)

有源区(TO)

Poly1(GT)

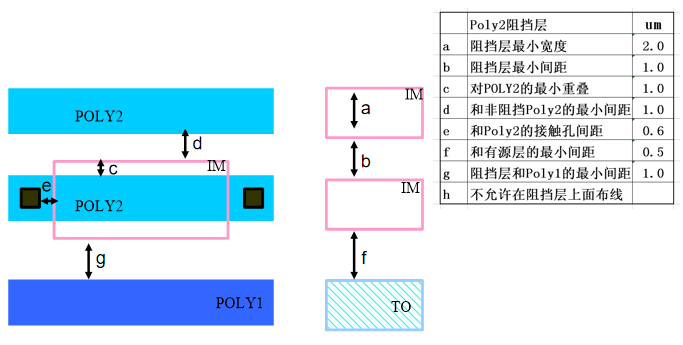

Poly2阻挡层(IM)

P+扩散区

N+扩散区

接触孔

金属层1

通孔

金属层2

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)