NC-verilog仿真工具使用(一)

一、介绍ncverilog是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step。基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作,ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看方式在仿真

参考:https://blog.csdn.net/qq_41467882/article/details/105870579

链接:https://pan.baidu.com/s/1ljHLUavTaEInp1Se5Wb11g

提取码:wv0f

一、介绍

nc verilog 是shell版的,nclaunch是以图形界面为基础的,二者调用相同内核;ncverilog的执行有三步模式和单步模式,在nclaunch中对应multiple step和single step。基于shell的ncverilog操作(尤其是单步模式)更适合于大批量操作,ncverilog的波形查看配套软件是simvision,其中包含原理图、波形、信号流等查看方式

在仿真以前,你必须编译和描述它。编译过程将把源文件中的用HDL编写的单元编译成内在的描述。描述设计将在设计的实例化,结构化信息的基础上建立设计的层次结构,建立信号的连接,计算所有对象的初始值。你编译,描述和仿真你的设计要用到以下的工具:

ncvlog: 编译Verilog源文件。

ncelab: 描述设计并且生成仿真的snapshot。

ncsim : 对snapshot进行仿真。

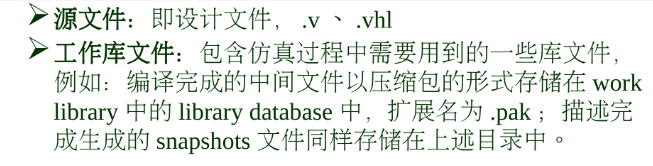

NC内部文件结构

- 源文件

- 工作库文件

- 配置文件:

- 仿真结果输出文件

二、仿真步骤

1.启动:

终端输入nclaunch,启动图形化界面,通过file>switch to single step切换单步或者多步模式。

file>set design directory设置工作目录

2.编译:

仿真你的设计以前,你必须用编译器编译源文件,并且用描述器(elaborator)把设计描述成snapshot的形式。Snapshot是仿真器将调用的你的设计的表述,它和其它由compiler和elaborator产生的中间目标一起保存在库中。

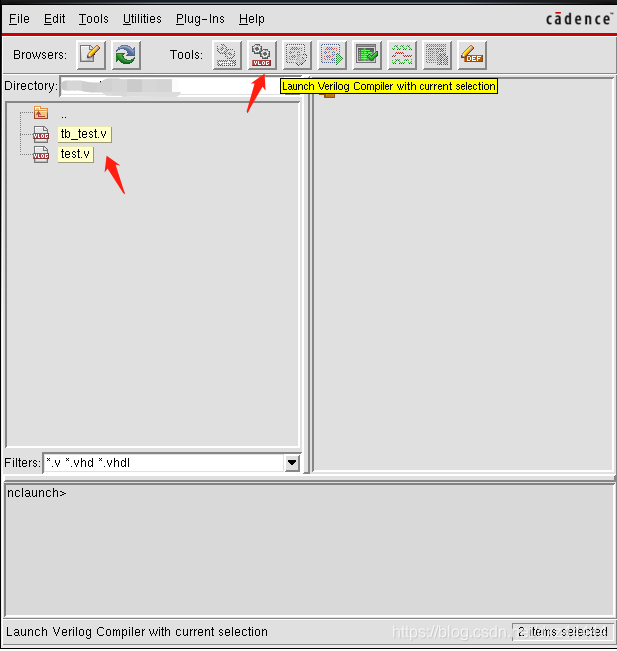

左边的窗口显示了当前目录下的所有的文件,在你编译和描述了设计以后,右边窗口就会显示设计的库。

选中在设计时建立的Verilog文件:要选择多个檔,需要按住Ctrl键并选中每个檔。

按下编译器按钮![]() :

:

在窗口底部的输入输出区域会显示由于你的选择而输入的命令和运行后的结果,同时它也显示了NC-Verilog在编译过程中的消息。(刷新界面之后)默认的,NC-Verilog将产生一个叫INCA_libs的目录以及一个叫worklib的目录。所有设计中的模块都将编译在worklib目录下面。注意INCA_libs现在就出现在了NCLauch左边的浏览器中,同时设计的库worklib也加入了库浏览器(右边窗口)中。

3.描述

展开库(worklib),选择顶层(top-level)的单元,然后选择描述(elabrate)按钮![]() 。

。

尽管如此,为了做一个指南,这里在你描述以前你必须设置一些选项。按照以下几步进行选项的选择然后描述你的设计:

1.通过点击加号展开工作库(worklib)

2.展开选择顶层设计单元,选择module

4.选择Tools- Elaborator以打开Elaborate模式

注意这里的Access Visibility按钮选中并且它的值是All,这个选项意味着全部存取(读,写,连接探测)来仿真目标,这样你就可以在仿真的数据库里面探测目标和范围,调试你的设计。

其它模块都没有定义时间表,为了防止elaborator报错,这里启动Other Option选项然后再文本框输入-timescale 1ns/1ns。

4.仿真

展开Snapshots文件夹,以显示在你的库中你可以选择的snapshot。选中你想要仿真的snapshot,按下仿真按钮![]()

设计浏览器(Design Browser)和控制窗口(Console window)就会出现。你可以在设计浏览器(Design Browser)中进入设计的各个层,你也可以在控制窗口(Console Window)输入命令来进入SimVision和Tcl Simulator。

Simvision把仿真定位在了各层的上面,同时给它定义了名字叫做Simulator。设计的各层的最高层就放置在了仿真的下面。

SimVison窗口让你可以输入SimVison的命令;仿真器(simulator)窗口让你可以输入Tcl simulator命令。在你运行仿真的时候,控制窗口(console window)同样会在SimVision和simulation窗口中显示消息。

三、设计仿真

SimVision让你控制和查询你的设计仿真。 可以帮助定位和特定的仿真事件相关的程序段。如果发现设计中有错误,可以直接编辑源文件,重新编译和描述,而不用离开SimVision的环境。

选择菜单Simulation--〉Create Probe(探针)

SimVision打开Probe的设置窗口,这个窗口允许你选择一层或者多层子范围,选择你要探测的信号类型, 然后记录探测信息到任何数据库。

设置probe的窗口

针对这个探测:

·选择Include sub-scopes下拉菜单中的all选项以包含所有设计的子域。

·选择Include within each scope下拉菜单中的all选项以包含输入,输出 和端口。

·取消选中Add to waveform display。

四、查看仿真结果

1.点击Waveform![]() 按钮,让这些信号在波形窗口(waveform window)中显示。

按钮,让这些信号在波形窗口(waveform window)中显示。

2.点击Waveform![]() 按钮,可以查看信号流向原理图

按钮,可以查看信号流向原理图

3.在Time Range 文本框中输入一个时间段. 在这个例子中,输入的是0:2000, 点击Enter键以应用新的时间段。在波形数据上方的下拉菜单中选择Keep this view ,这样你就可以保存你的缩放设置。 任意时刻,你能通过下拉菜单选择来快速地回到显示这个缩放段。

最右边:+ 、-、= ,用来波形缩放查看

4.,定位探测点具体时间

在波形窗口(waveform window)中有两个指标,分别叫做TimeA和Baseline。可以把它们移到仿真时间的任意点,然后以它们为参考点。

输入一个新的仿真时间,然后enter:

·拖动指标到你想要探测的时间点,也可以在指标时间输入文本框中输入一个仿真时间来实现目的。

5.修改代码错误

利用SimVision按照以下的步骤来查找有源文件有错误的地方:

在波形窗口(waveform window),选择变量然后选择打开源浏览器(source browser)。CTRL+W可查看波形

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)