异步FIFO(clkw<=clkr),最小深度计算

异步FIFO(clkw<=clkr),最小深度计算前言一、如何计算?1.clkw/clkr>=32.2clkw/clkr>=3,且clkw/clkr<33.3clkw/clkr=3总结前言一开始,我简单的认为写时钟频率(clkw)小于等于读时钟频率(clkr)的时候,FIFO深度为1即可,但事实证明我理解有误.一、如何计算?push之后,写指针w_code在下一拍更新,但同

异步FIFO(clkw<=clkr),最小深度计算

前言

一开始,我简单的认为写时钟频率(clkw)小于等于读时钟频率(clkr),也就是写时钟周期(Tw)大于读时钟周期(Tr)的时候,FIFO深度为1即可,但事实证明我理解有误.

一、如何计算?

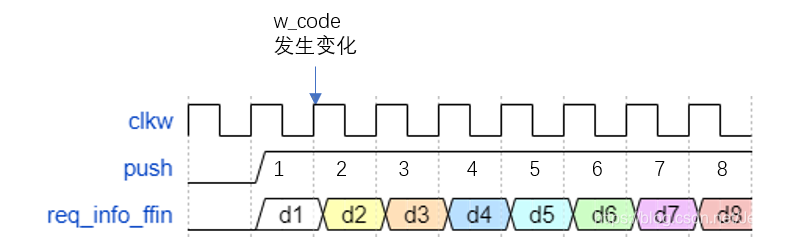

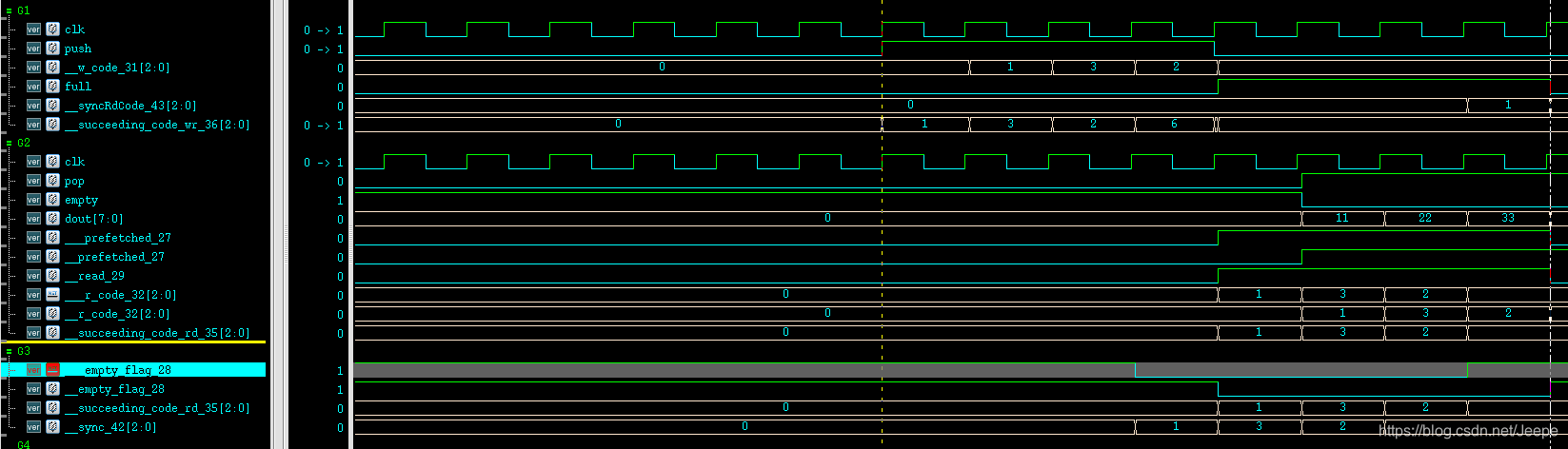

push之后,写指针w_code在下一拍更新,但同步到读时钟域,经常的做法是打两拍,这时,空信号拉低,非空即可pop数据,那么,读指针则在第三个clk_r上升沿更新,再同步到写时钟域,则需要打两拍。所以,在满足clkw<=clkr的前提下,则可分为三种情况:

1. Tw/Tr>=3

这种情况即是在一个Tw周期期间,读指针已经变化(前面提及“读指针则在第三个clk_r上升沿更新”)【其中,第几个clk_r是相对于第一个push后的下一个clk_w上升沿,即上图中w_code处】,也就是说push过后的第二个写时钟周期期间读指针发生了变化(前提:非空就pop数据),那么,读指针同步两拍到写时钟域,也就是第4个写时钟期间,读指针已经同步过来了,那么,这种情况下,FIFO深度只要大于等于4即可使FIFO不产生full信号

2. 2Tw/Tr>=3,且Tw/Tr<3

这种情况即是在两个Tw周期期间,读指针发生变化,也就是说push过后的第三个写时钟周期期间读指针发生了变化,那么,读指针同步两拍到写时钟域,也就是第5个写时钟期间,读指针已经同步过来了,那么,这种情况下,FIFO深度只要大于等于5即可使FIFO不产生full信号

3. 3Tw/Tr=3

这种情况即是在3个Tw周期期间,读指针发生变化,也就是说push过后的第4个写时钟周期期间读指针发生了变化,那么,读指针同步两拍到写时钟域,也就是第6个写时钟期间,读指针已经同步过来了,那么,这种情况下,FIFO深度只要大于等于6即可使FIFO不产生full信号

总结

在满足前提条件的情况下(clkw<=clkr,非空就pop数据),FIFO最小深度为:n+3。其中,n为使条件(nTw/Tr>=3)满足的最小的n。还有一些设计对empty做了打一拍处理,那么,也就导致了读指针则在第4个clk_r上升沿更新,也就导致了,n为使条件(nTw/Tr>=4)满足的最小的n。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)