Quartus ii 软件仿真基本流程(使用VHDL)

Quartus ii 软件仿真基本流程(使用VHDL)文章首发于我的个人博客这是VHDL系列教程的第一个教程。所谓教程,其实也就是记录我本人在学习过程中遇到的问题和学习内容的笔记,分享在这里供其他初学者参考,如果博客中出现任何错误或不严谨的地方,您可以在下方评论区指出来,您的反馈是对我最大的帮助,万分感谢。这篇博客主要介绍使用Quartus ii软件进行仿真的步骤,由于是第一篇所以过程详细但有些冗

文章首发于我的个人博客

这是VHDL系列教程的第一个教程。所谓教程,其实也就是记录我本人在学习过程中遇到的问题和学习内容的笔记,分享在这里供其他初学者参考,如果博客中出现任何错误或不严谨的地方,您可以在下方评论区指出来,您的反馈是对我最大的帮助,万分感谢。

这篇博客主要介绍使用Quartus ii软件进行仿真的步骤,由于是第一篇所以过程详细但有些冗余(问题不大),之后的教程应该专注于VHDL语言本身以及Quartus ii的一些使用技巧。

本教程将用VHDL实现D触发器来走一遍Quartus ii仿真的流程。

首先,打开Quartus ii仿真软件,新建一个工程。

点击Next;

这三个名称都应该相同;

与上一步的文件名也相同;

这里需要选择要编译对应的硬件设备。但是如果不用FPGA硬件仿真可以直接默认,对方真影响不是很大,但如果学校有FPGA板子则尽量选择板子对应的型号;

工程新建完成之后,再创建一个VHDL文件;

如果刚刚新建的VHDL没有保存,可以再File里选择另存为;

VHDL文件名和工程名相同;

在刚刚新建的VHDL文件中写入D触发器的实现代码(这里不做代码的讲解),然后点击小三角选择编译;

-- D trigger achievement

library ieee;

use ieee.std_logic_1164.all;

ENTITY Dtrigger IS PORT(

D, clk : IN STD_LOGIC;

Q : OUT STD_LOGIC

);

END ENTITY Dtrigger;

ARCHITECTURE one of Dtrigger is

SIGNAL sig_save : STD_LOGIC;

BEGIN

PROCESS(clk)

BEGIN

if clk'event and clk='1' then

-- == rising_edge(clk) then

sig_save <= D;

end if;

END PROCESS;

Q <= sig_save;

END ARCHITECTURE one;

新建一个波形仿真文件;

新建波形仿真文件之后,在Edit中选择End Time设置仿真终止时间,默认为1us,时间有点短,改大一点;

在这里我设置为51us;

可以使用Ctrl+滚轮放缩。之后双击Name区域导入变量;

点击list按钮就会显示出Entity(实体)定义的所有变量,之后全部导入即可;

之后在波形文件中画出clk时序波形和输入变量D的波形,在画的时候我的经验是选择左下角的Grid,这样跟容易画;

在Processing下拉菜单的Simulator Tool里选择仿真方式;

选择Timing,即时序仿真;选择Functional,即功能仿真;这里选择Timing;

点击波形仿真按钮;仿真结束可以在仿真图里看到,当clk时钟信号为上升沿的时候,输出信号Q会随输入信号D的变化而变化,clk时钟信号为0的时候,保持原状态;

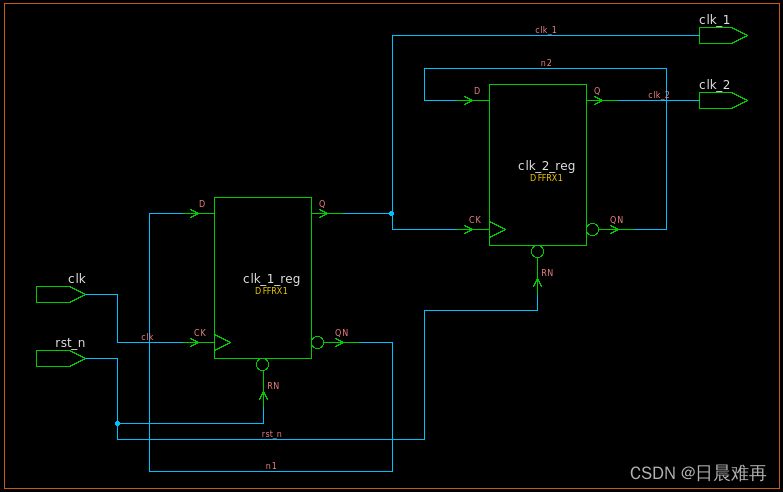

选择Tools下拉菜单里的Netlist Viewers–>RTL Viewer可以查看VHDL描述的硬件电路。(其实在VHDL编译之后就可以查看)

硬件电路如下图所示。

好的,以上就是本篇教程的全部内容了,以后的教程跟多的内容会是VHDL语言本身以及Quartus ii的使用技巧了。

End.

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)