Altium Designer 原理图的编译与检查

将原理图更新到PCB之前需要对原理图进行编译以及电气性能的检查,可以利用AD自带的ERC功能对原理图进行检查原理图的编译:原理图界面选择菜单栏的:工程---->Compile PCB Project接着可以在右下角,点击panels---->Message,就可以打开Message界面...

将原理图更新到PCB之前需要对原理图进行编译以及电气性能的检查,可以利用AD自带的ERC功能对原理图进行检查

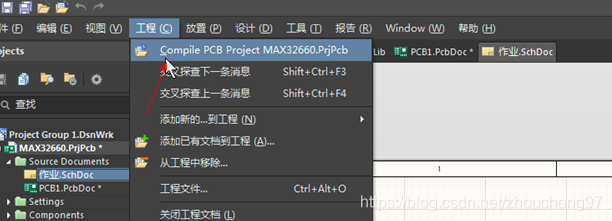

原理图的编译:

原理图界面选择菜单栏的:工程---->Compile PCB Project

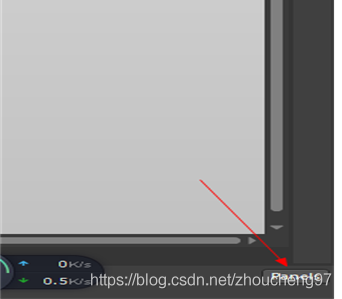

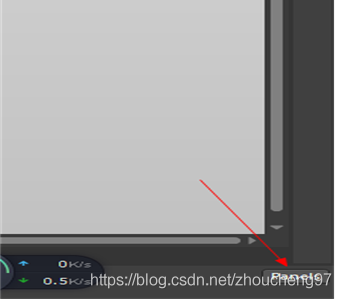

接着可以在右下角,点击panels---->Message,就可以打开Message界面

操作到这里,原理图就检查成功了,用户需要对Message面板的错误信进行修改(修改指的是修改你的原理图),知道修改完才算完成原理图的修正

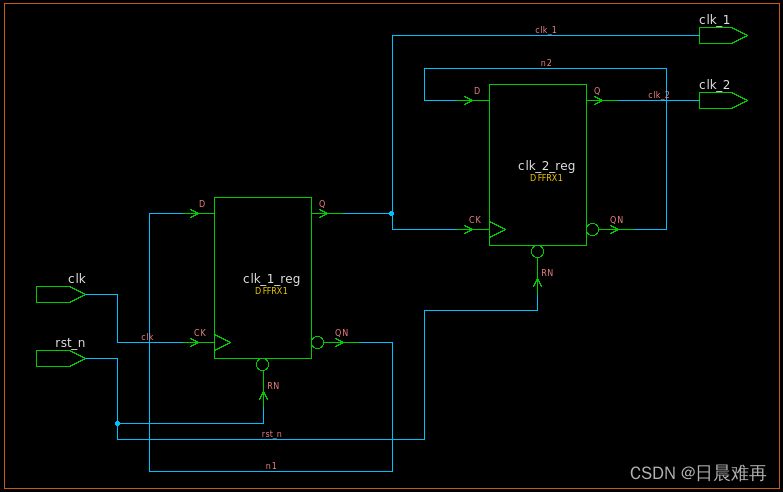

原理图的常用检测:

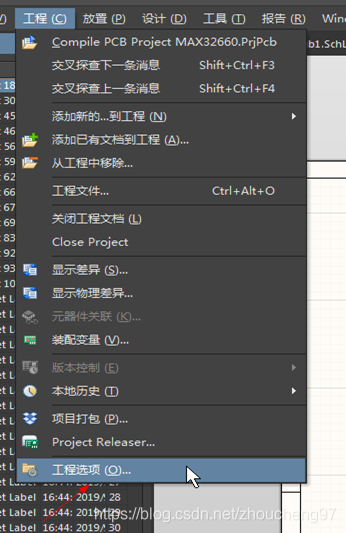

原理图界面选择菜单栏的:工程---->工程选项

点击之后我们可以看到对应的信息,所有与项目有关的选项都会在此对护框中设置

特别注意:用户不要随便修改系统默认的检查=项报告格式,除非用户很清楚这些检测项

最后,列一下常见的原理图错误

1、Duplicate Part Designators :存在重复的元件位号

2、Floating Net Labels :网络悬浮

3、Floating Power Objects :存在悬浮的电源端口

4、Nets with only one pin :存在单端网络

5、Net with multiple names:网络名重复

6、Off grid object:对象没有处在栅格点的位置

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)