Quartus ii 与 Verilog入门教程(1)——Verilog实现8位计数器

1.计数器原理在时钟作用下,输出信号从0开始,每个时钟的上升沿输出加1。当复位信号有效时,输出清零。计时实现只需累加即可。计数器虽然简单,但是在多种场合都有应用,比如产生ROM地址、分频、状态机等。比如:Matlab与FPGA数字信号处理系列——DDS信号发生器——Quartus ii 利用 ROM 存储波形实现DDS(1)2.代码编写(1)新建工程第一页配置工程存放路径、工程名、顶层...

下载:Quartus ii与verilog实现8位计数器,Modelsim仿真工程

1.计数器原理

在时钟作用下,输出信号从0开始,每个时钟的上升沿输出加1。当复位信号有效时,输出清零。计时实现只需累加即可。

计数器虽然简单,但是在多种场合都有应用,比如产生ROM地址、分频、状态机等。

比如:

Matlab与FPGA数字信号处理系列——DDS信号发生器——Quartus ii 利用 ROM 存储波形实现DDS(1)

2.代码编写

(1)新建工程

第一页配置工程存放路径、工程名、顶层文件名,点Next;

第二页直接点Next;

第三页选择FPGA型号,飓风4系列 EP4CE6F17C8;

第四页配置仿真软件和语言,此处设置为使用 Modelsim-Altera 仿真,语言选择Verilog语言,对下图中的Modelsim-Altera,如果没有使用Modelsim的Altera自带的定制版,使用的是Modelsim SE,那么此处选择Modelsim;

第五页直接点Finish,工程如下图所示。

(2)新建Verilog顶层文件

(3)编写Verilog代码,保存为count.v文件

| 引脚 | 特性 | 功能 |

|---|---|---|

| clk | 输入——时钟 | 仿真中设置为100M,上升沿有效 |

| rst_n | 输入——复位 | 低电平有效,计数值清零 |

| count_out | 输出——计数值 | 位宽8-bit,从0计数到255,时钟上升沿+1 |

module count(

clk,

rst_n,

count_out

);

input clk;

input rst_n;

output reg [7:0] count_out;

always @ ( posedge clk or negedge rst_n )

begin

if( !rst_n ) begin

count_out <= 8'b0;

end

else begin

count_out <= count_out + 1'b1;

end

end

endmodule

(4)编译工程

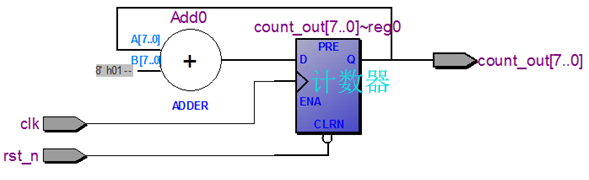

点击 RTL Viewer可以看代码综合后的RTL 电路;

可以看到,代码被综合成带有使能和清零的D触发器和加法器,每个时钟加8’h01(十六进制的1,位宽8-bit);

3.Modelsim仿真

(1)生成 Test Bench 测试文件

(2)打开Test Bench 文件并添加到工程

点击文件夹标志,弹出的对话框中找到 simulation 文件夹下的modelsim 文件夹,打开 modelsim 文件夹,将文件类型选为“All Files”,并把下方的“Add file to current project”勾选上;

(3)编写激励信号

将 count.vt 文件的内容用以下代码代替:

`timescale 1 ns/ 1 ps

module count_vt();

reg clk;

reg rst_n;

wire [7:0] count_out;

count i1 (

.clk(clk),

.count_out(count_out),

.rst_n(rst_n)

);

initial

begin

clk = 0;

rst_n= 0;

#20;

rst_n= 1;

#600;

$stop;

$display("Running testbench");

end

always

begin

#5 clk = ~clk;

end

endmodule

(4)配置仿真

右键1处,选 setting,再选择 2 处,勾选 3 处后点击 4 处;

弹出的对话框,点击1处,弹出第二个对话框,在2处输出仿真文件中的模块名称“count_vt”,点击3处,找到simulation->modelsim-> count.vt 文件并添加“Add”,点击三次“OK”;

对下图1处的Modelsim-Altera,如果没有使用Modelsim的Altera自带的定制版,使用的是Modelsim SE,那么此处选择Modelsim;

(5)开始仿真

点击下图中的图标,会调用 Modelsim 仿真;

4.仿真结果

复位为0时输出为0,复位为1后,在时钟clk的上升沿输出加1;

箭头所指白色的输出信号,右键 Radix -> Unsigned,可以输出无符号整数,8位输出可以表示0~255;

点击红框内的,可以设置继续仿真的时间,后面可以点击仿真指定时间、停止等;

欢迎关注:FPGA探索者

回复“8位计数器”获取工程及源码。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)