三输入的多数表决器

**计算机组成原理——多数表决器**题目:设计3输入的多数表决器分析:多数表决器原理相当于投票,多数胜于少数。一般即3局2胜,5局3胜,以此类推。一:确定输入输出。二:画出真值表。三:根据真值表写出输出表达式,并化简。四:画出电路图。五:在logism确定电路是否正确,然后再在实验箱上验证即可。*以上为分析电路的基本思路,但不是每一项都是必要的,如五:logism上验证以及实验箱...

计算机组成原理——多数表决器

题目:设计3输入的多数表决器

分析:多数表决器原理相当于投票,多数胜于少数。一般即3局2胜,5局3胜,以此类推。

一:确定输入输出。

二:画出真值表。

三:根据真值表写出输出表达式,并化简。

四:画出电路图。

五:在logism确定电路是否正确,然后再在实验箱上验证即可。*

以上为分析电路的基本思路,但不是每一项都是必要的,如五:logism上验证以及实验箱上验证有条件即可尝试。

1.此题为3输入的表决器,故有三个输入,可分别设为A,B,C,输出设为F。字母根据个人设置,但都应该大写。

2真值表

可能会有像我一样刚开始不知道用啥画真值表。

我一般用的wps,这边就简易介绍一下,如果有大佬有更简便的方法,请不吝赐教,万分感谢。

打开wps后直接新建文档,点击插入——表格。选择所需要的行列,然和合并,扩展即可。

合并操作:选择要合并的格子,单击右键,点击合并即可。

3.根据真值表写出输出表达式

F=AB+AC+BC //可用狄摩根律转化为与非形式。

过程:写输出表达式即把输出结果为一的输入相加。如上F的一的有四个,把结果为一对应的输入写出即可,再化简,可通过卡诺图以及逻辑表达式化简。若此步有不清楚的可留言。

4.画出电路图

这个电路图可用logism画,特方便,还可以检查结果是否正确。 直接在浏览器搜索即可,但是配置环境jdk,教程里面有。如有问题,可随时留言。

五:logism中画图如下:

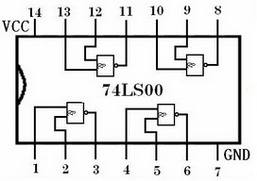

实验箱验证:根据所给的芯片设置,查阅其引脚图,连接线路即可。如用74ls00芯片。

由于一个芯片有四个与非门,八个输入,我们只要三输入,两个与非门,随便选择两个与非门,应有四个输入,我们只用三个,但必须四个都接,由于与非门0决定输出,故另一个输入给接一个1不影响结果

以上是我对三输入表决器的理解,由于水平有限,如有错误,请大佬们精确指正。如有疑问,欢迎留言。

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

所有评论(0)