简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

HSV(huesaturation value)色调(hue):对应于颜色成分(基础色素),因此,只需选择一个色调范围,就可以选择任何颜色。(0—360)饱和度(saturation):颜色的数量(颜料的深度)(主导色调)(0—100%)值(value):颜色的亮度。(0—100%)1、学习目标使用HSV色彩空间进行物体检测和物体跟踪2、函数方法(1)使用色调饱和度值(HSV)...

绘制的梯形图背景为灰色,这表明梯形图处于编辑中状态梯形图编辑完成后,要进行变换菜单栏->转换 /编译->转换转换成功后,背景为白色在变换过程中出现报错的情况,说明梯形图中有错误,光标移动到梯形图出错部位,请检查梯形图。...

数组声明非组合型(unpacked)特点:消耗更多的存储空间,但是更易于查找元素对于Verilog,数组经常会被用来做数据存储,例如reg [15:0] RAM [0:4095] ;//存储数组SV将Verilog这种声明数组的方式称之为非组合型声明,即数组中的成员之间存储数据都是互相独立的。Verilog也不会指定软件去如何存储数组中的成员。wire [7:0] table [3:0];SV保留

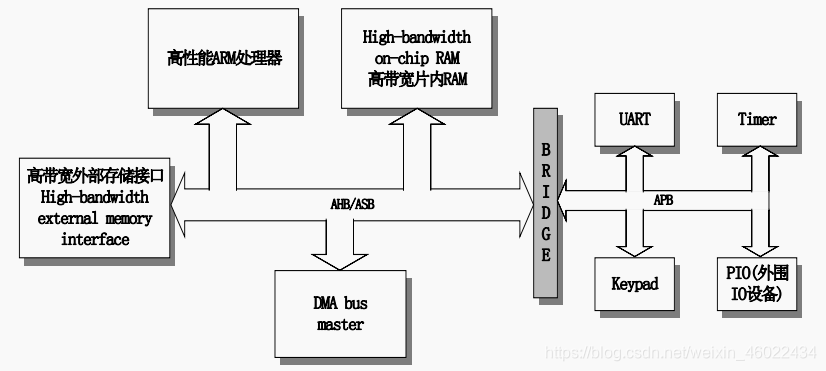

AMBA AHB 是一种适用于高性能可综合设计的总线接口。它定义了组件之间的接口,例如主设备、互连设备和从设备。

计数器逻辑功能对输入时钟脉冲进行计数也可用于分频、定时、产生节拍脉冲等分类按时钟输入方式,分为同步和异步计数器按进位体制,分为二进制、十进制和任意进制计数器按计数方向,分为加法、减法和可逆计数器计数器的“模”(Modulo)计数器运行时,依次遍历规定的各状态后完成一次循环,它所经过的状态总数称为计数器的“模”,通常用M表示。例子:一个2位的二进制计数器循环输出00、01、10和11,称为模4计数器

第1章 引言解释了什么是静态时序分析以及它如何用于时序验证。还描述了功率和可靠性方面的考虑。概述了纳米设计的静态时序分析程序。本章解决了诸如什么是静态时序分析、噪声和串扰的影响是什么、如何使用这些分析以及这些分析适用于整个设计过程的哪个阶段等问题。1.1纳米设计在半导体器件中,金属互连迹线通常用于在电路的各个部分之间建立连接以实现设计。随着工艺技术的缩小,众所周知,这些互连走线会影响设计的性能。对

绝对零基础开始┭┮﹏┭┮1、基础准备前期基础准备参考《数字后端学习ing》中1-5数字ic后端学习ing2、学习芯片开发所需要的环境Linux环境EDA工具:3、Verilog以下划分,根据自己目前学习的感觉划分的, 仅作参考初级——了解Verilog 语法学习参考视频:B站 Verilog零基础入门、6小时掌握Verilog语法(Verilog语法入门)学习内容整理:(自己根据学习视频记录的笔记

第 3章 标准单元库(Standard Cell Library)描述了常用库单元描述中的时序相关信息。本章仅关注与时序、串扰和功率分析相关的属性,尽管库单元包含多个属性。纳米技术中对时序的主要影响是互连。除了时序信息外,库单元描述还包含几个属性(attributes),如单元面积和功能,这些属性与时序无关,但在RTL合成过程中相关。在本章中,我们只关注与时序和功率计算相关的属性(attribut

第 8 章 时序验证(Timing Verification)描述了时序检查,这个各种时序检查是作为各种时序分析的一部分执行。其中包括amongst others - setup、保持和异步恢复和移除检查。这些时序检查旨在彻底验证被分析设计的时序。本章节将介绍静态时序分析所执行的一部分检查,这些检查旨在详尽地验证待分析设计的时序。两个主要检查是建立时间检查和保持时间检查。一旦在触发器的时钟引脚上定

第 10 章 稳健验证(Robust Verification)介绍一些高级关键的主题,比如说on-chip variation, time borrowing, hierarchical methodology, power management 和statistical timing analysis。本章描述了特殊的 STA 分析,例如时间借用( time borrowing)、时钟门控(c