简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

数字图像2D降噪算法

由于I /O单元和模块的布放已经在布图规划时完成,因此布局的剩余任务主要是对标准单元的布局。

在研读了论文及开源代码后,对LOAM的一些理解做一个整理。文章:Low-drift and real-time lidar odometry and mapping开源代码:https://github.com/daobilige-su/loam_velodyne系统概述LOAM的整体思想就是将复杂的SLAM问题分为:1. 高频的运动估计; 2. 低频的环境建图。Lidar...

说明:介绍如何调整机器人上的ROS导航包步骤:(1) 机器人导航需要那些准备?在调整新机器人上的导航包时遇到的大部分问题都在本地规划器调谐参数之外的区域。机器人的里程计,定位,传感器以及有效运行导航的其他先决条件常常会出错。所以,我做的第一件事是确保机器人本身正在准备好导航。这包括三个组件检查:距离传感器,里程计和定位。距离传感器如果机器人没有从其距离传感器(例如激光器)...

在相同版本间的ROS进行通信不在赘述了,修改/etc/hosts文件即可。最近项目遇到在Ubuntu16.04 与Ubuntu18.04两个系统间进行ROS通信,ROS版本分别为Kinetic和Melodic。配置网络后,两边都能够ping通,但是在获取ros数据是,却出现报错:后面在ROS wiki上查询到相关解决方案:即:Master: export ROS_HOST...

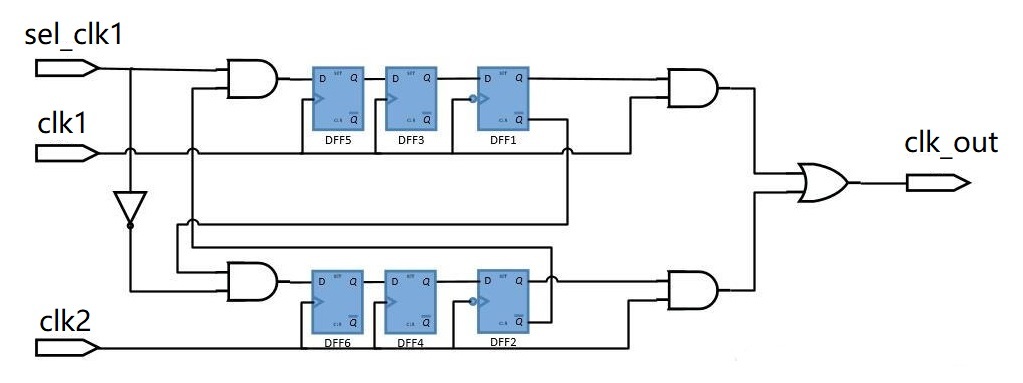

随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且同步的,也有可能是不相关的。直接使用选择逻辑进行时钟切换大概率会导致分频时钟信号出现毛刺现象,所以时钟切换逻辑也需要进行特殊的处理

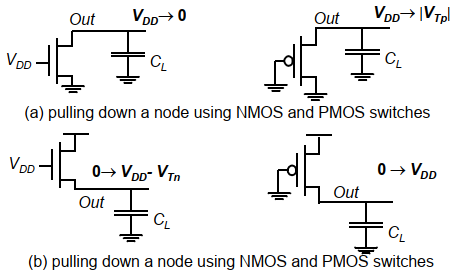

介绍了静态互补CMOS逻辑

一、多时钟周期 multicycle paths在一些情况下,如下图所示,两个寄存器之间的组合电路传输的逻辑延时超过一个时钟周期。在这样的情况下,这个组合路径被定义为多周期路径(multicycle path)。尽管后一个寄存器会在每一个的时钟的上升沿尝试捕获(capture)数据,但我们会在STA中指定个时钟周期后的上升沿(relevant capture edge)去捕获数据。以上图为例,组合

CSI(Camera Serial Interface)定义了摄像头外设与主机控制器之间的接口,旨在确定摄像头与主机控制器在移动应用中的标准。

工艺库相关信息