简介

该用户还未填写简介

擅长的技术栈

可提供的服务

暂无可提供的服务

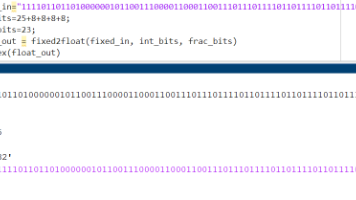

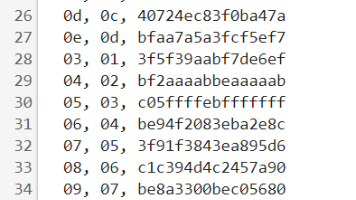

本文介绍了怎么在MATLAB中使用单精度浮点数进行运算,另外还将MATLAB单精度浮点数运算的结果和VIVADO浮点数IP核运算的结果作了对比,会发现二者结果是吻合的。最后还介绍了怎么在MATLAB中进行定点运算的仿真,也将其和VIVADO仿真的结果进行了对比,二者也是吻合的。

在FPGA上实现算法时,相比MATLAB实现往往需要更长的开发周期,且调试过程更为复杂。因此,可以先用MATLAB对基于FPGA的定点和浮点运算的算法进行仿真验证,只要仿真结果正确,在FPGA上实现时通常只需解决资源和时序问题即可。笔者在仿真算法时,需要模拟一个定点转浮点的IP核功能,为此专门编写了MATLAB定点转浮点转换函数。

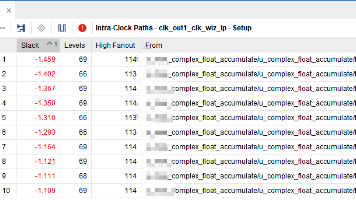

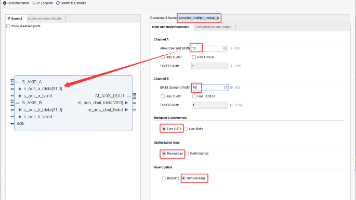

在使用 Vivado 设计时,IP 核配置是影响综合结果和时序性能的关键因素之一。特别是在涉及高速数据处理或对延迟敏感的应用场景中,Vivado IP 核常常提供 “High Speed” 与 “Low Latency” 两种优化选项。很多开发者在配置IP核时往往忽略了这些选项对实际时序性能的深远影响。本文将以实际示例出发,对比分析 Vivado 中Accumulator Floating Poi

在 FPGA 开发过程中,合理设定寄存器或存储器(如 BRAM、ROM)的初始值对于系统功能验证与上电行为控制至关重要。许多设计者习惯使用复位信号对寄存器或存储器进行初始化。然而,依赖复位并非总是最优解。复位逻辑会增加额外的资源开销,拉长时序路径,甚至在复杂设计中影响时钟收敛。我们可以利用 Vivado 提供的“赋初值”方法,在 HDL 代码中直接为寄存器和存储器设置上电初值,该方法能确保电路在上

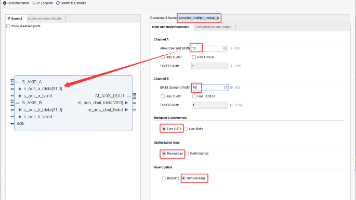

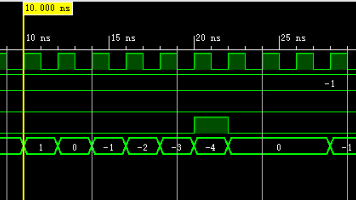

在现代数字信号处理和通信系统中,对数据进行快速而精确的累加操作是至关重要的。Vivado Accumulator IP核提供了一种灵活、可配置的硬件累加方案,用于在FPGA上实现数据的累加法(也可以配置为累减)操作。本文详细介绍了IP核配置选项,并编写verilog代码测试了该IP核的累加功能。

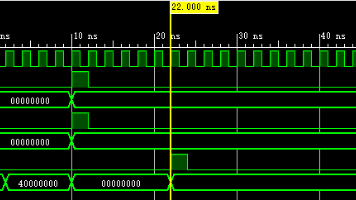

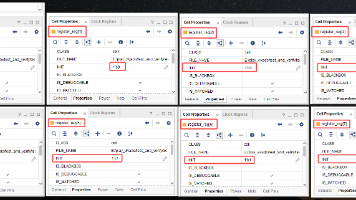

在数字信号处理、通信系统以及其他嵌入式应用中,复数运算是不可或缺的基础。Vivado设计套件作为Xilinx公司的一款强大工具,提供了丰富的IP核,其中复数乘法器(Complex Multiplier)是实现高效复数运算的重要组件。本文将说明Vivado IP核中的定点复数乘法器(Complex Multiplier)的使用方法,介绍该IP核的配置选项,并编写verilog代码测试了该IP核的累加

在使用 Xilinx Vivado 进行 FPGA 开发时,如何将 RTL 仿真生成的数据导出,进行进一步分析与可视化,是很多开发者常遇到的问题。Vivado自带仿真工具不支持直接导出仿真数据,但是我们可以通过编写一段简单的RTL代码即可将需要的仿真数据保存到txt文件中,后续MATLAB有自带的的textscan函数可以将txt中的数据读出来,本文将详细介绍这一过程。

VIVADO中编写完程序上板测试时经常会用到viavdo自带的ILA逻辑分析仪IP核,在ILAIP核的产品手册中,明确说明采样时钟必须为永不停息的时钟,也就是只能是系统时钟或PLL、MMCM分频倍频出来的时钟,用户通过时序逻辑分频的时钟是无法使用的,这就造成了在采样深度有限情况下无法完整采集频率较低的数据,使用起来不方便,本文章介绍ILA的进阶使用,结合VIOIP可以任意改变ILA的采样频率且不会

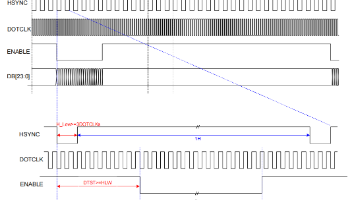

ILI9488是一款广泛应用于嵌入式系统和电子设备的彩色TFT LCD显示控制器芯片。本文将介绍ILI9488关于RGB接口的时序和相关的一些配置,笔者多次阅读芯片手册多次调试之后最终成功用FPGA点亮了一块分辨率为320*320的ILI9488驱动的TFT LCD显示屏,实现了稳定的RGB三基色显示功能,分别显示了RGB三基色图片。SPI初始化后,即可用RGB接口来传输像素值。

在数字信号处理、通信系统以及其他嵌入式应用中,复数运算是不可或缺的基础。Vivado设计套件作为Xilinx公司的一款强大工具,提供了丰富的IP核,其中复数乘法器(Complex Multiplier)是实现高效复数运算的重要组件。本文将说明Vivado IP核中的定点复数乘法器(Complex Multiplier)的使用方法,介绍该IP核的配置选项,并编写verilog代码测试了该IP核的累加